©2008 Advanced Micro Devices, Inc.

IOXAPIC Registers

AMD SB600 Register Reference Manual Proprietary Page 296

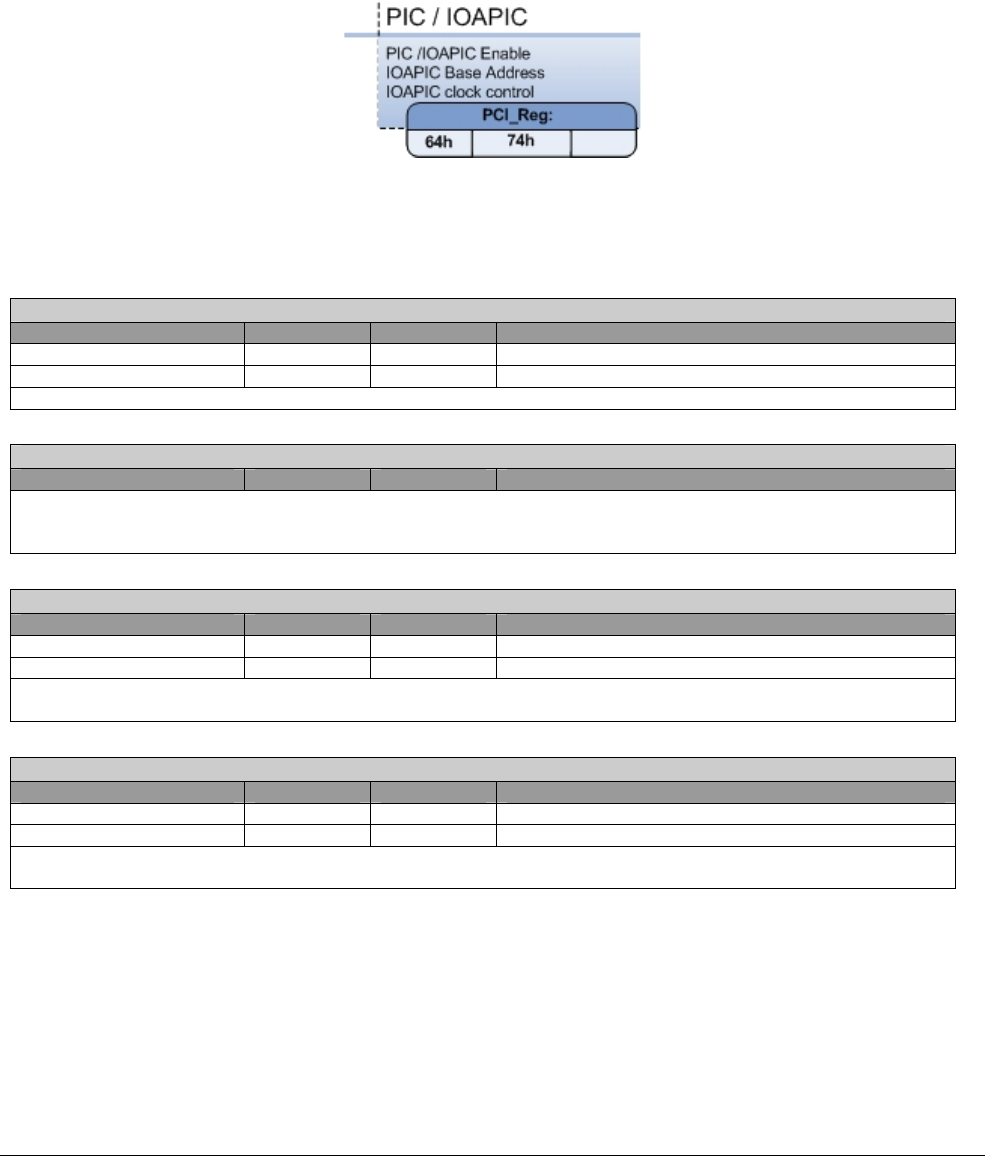

4.5 IOXAPIC Registers

Note: Some IOXAPIC functions are controlled by, and associated with, certain PCI configuration registers in

the SMBus/ACPI device. For more information refer to section 2.3: SMBus Module and ACPI Block (Device

20, Function 0). The diagram below lists these IOXAPIC functions and the associated registers.

4.5.1 Direct Access Registers

Note: The XAPIC_BASE_REGISTER has a power-on default value of FEC0_0000H.

IO Register Select Register RW [XAPIC_BASE_REGISTER + 00H]

Field Name Bits Default Description

Indirect Address Offset 7:0 00h Indirect Address Offset to IO Window Register

Reserved 31:8

Used to determine which register is manipulated during an IO Window Register read/write operation.

IO Window Register RW [XAPIC_BASE_REGISTER + 10H]

Field Name Bits Default Description

Mapped by the value in the IO Register Select Register, to the designated indirect access register.

Technically a R/W register; however, the read/write capability is determined by the indirect access register

referenced by the IO Register Select Register.

IRQ Pin Assertion Register RW [XAPIC_BASE_REGISTER + 20H]

Field Name Bits Default Description

Input IRQ 7:0 00h IRQ number for the requested interrupt

<reserved> 31:8 0000000h

Write to this register will trigger an interrupt associated with the redirection table entry referenced by the IRQ

number. Currently the redirection table has 24 entries. Write with IRQ number greater than 17H has no effect.

EOI Register W [XAPIC_BASE_REGISTER + 40H]

Field Name Bits Default Description

Vector 7:0 00h Interrupt vector

<reserved> 31:8 0000000h

Write to this register will clear the remote IRR bit in the redirection table entry found matching the interrupt vector.

This provides an alternate mechanism other than PCI special cycle for EOI to reach IOXAPIC.