©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 69

Table 2-4 HceInput Registers

HceInput – RW - 32 bits

Field Name Bits Default Description

InputData 7:0 00h This register holds data that is written to I/O ports 60h and 64h.

Reserved 31:8 Reserved

I/O data that is written to ports 60h and 64h is captured in this register when emulation is enabled. This

register may be read or written directly by accessing it with its memory address in the Host Controller’s

operational register space. When accessed directly with a memory cycle, reads and writes of this register

have no side effects.

HceOutput Register

Table 2-5 HceOutput Register

HceOutput – RW - 32 bits

Field Name Bits Default Description

OutputData 7:0 00h This register hosts data that is returned when an I/O read of port 60h

is performed by application software.

Reserved 31:8 Reserved

The data placed in this register by the emulation software is returned when I/O port 60h is read and

emulation is enabled. On a read of this location, the OutputFull bit in HceStatus is set to 0.

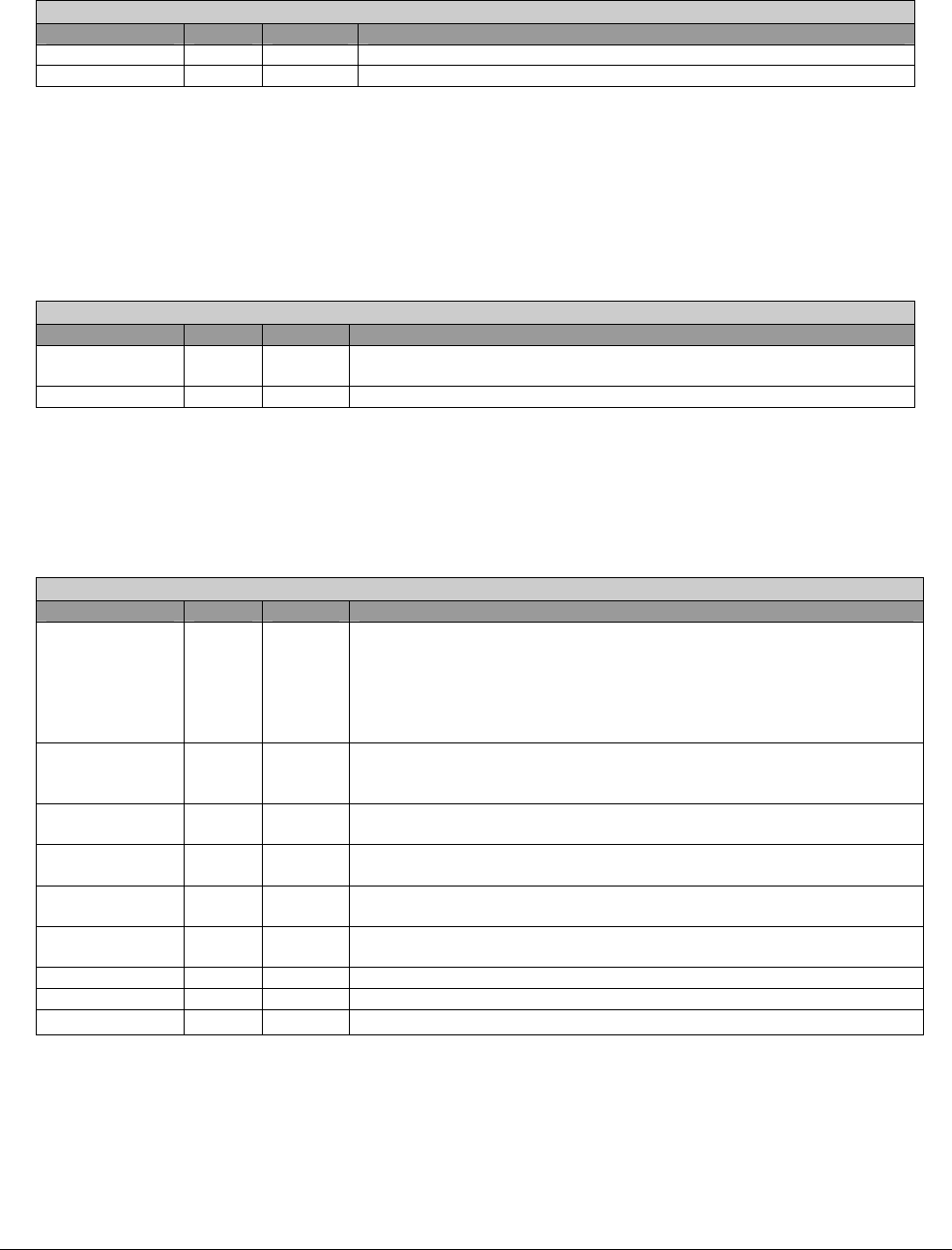

HceStatus Register

Table 2-6 HceStatus Register

HceStatus – RW - 32 bits

Field Name Bits Default Description

OutputFull 0 0b The HC sets this bit to 0 on a read of I/O port 60h. If IRQEn is set and

AuxOutputFull is set to 0, then an IRQ1 is generated as long as this bit

is set to 1. If IRQEn is set and AuxOutputFull is set to 1, then an IRQ12

is generated as long as this bit is set to 1. While this bit is 0 and

CharacterPending in HceControl is set to 1, an emulation interrupt

condition exists.

InputFull 1 0b Except for the case of a Gate A20 sequence, this bit is set to 1 on an

I/O write to address 60h or 64h. While this bit is set to 1 and emulation

is enabled, an emulation interrupt condition exists.

Flag 2 0b Nominally used as a system flag by software to indicate a warm or cold

boot.

CmdData 3 0b The HC sets this bit to 0 on an I/O write to port 60h and to 1 on an I/O

write to port 64h.

Inhibit Switch 4 0b This bit reflects the state of the keyboard inhibit switch and is set if the

keyboard is NOT inhibited.

AuxOutputFull 5 0b IRQ12 is asserted whenever this bit is set to 1 and OutputFull is set to 1

and the IRQEn bit is set.

Time-out 6 0b Used to indicate a time-out

Parity 7 0b Indicates parity error on keyboard/mouse data.

Reserved 31:8 Reserved

The contents of the HceStatus Register are returned on an I/O Read of port 64h when emulation is enabled.

Reads and writes of port 60h and writes to port 64h can cause changes in this register. Emulation software

can directly access this register through its memory address in the Host Controller’s operational register

space. Accessing this register through its memory address produces no side effects.