©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 32

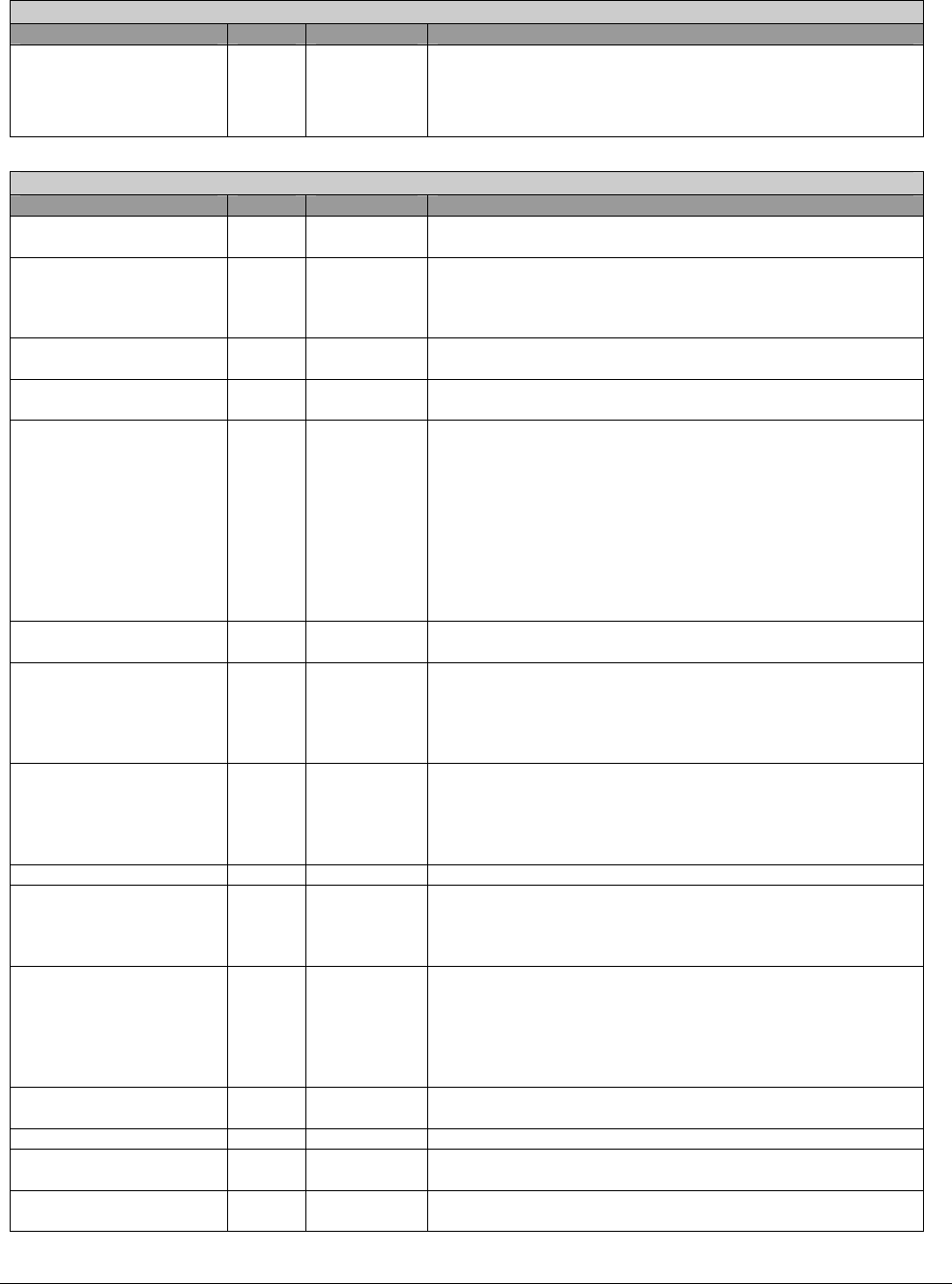

Port-N FIS Base Address Upper –RW – 32 bits [Mem_reg: ABAR + port offset + 0Ch]

Field Name Bits Default Description

FIS Base Address Upper

(FBU)

31:0 0000_

0000h

Indicates the upper 32-bits for the received FIS base physical

address for this port.

This register shall be read only ‘0’ for HBAs that do not

support 64-bit addressing.

Port–N Interrupt Status - RW - 32 bits [Mem_reg: ABAR + port offset + 10h]

Field Name Bits Default Description

Device to Host Register

FIS Interrupt (DHRS)

0 0b A D2H Register FIS has been received with the ‘I’ bit set, and

has been copied into system memory.

PIO Setup FIS Interrupt

(PSS)

1 0b A PIO Setup FIS has been received with the ‘I’ bit set, it has

been copied into system memory, and the data related to that

FIS has been transferred. This bit shall be set even if the

data transfer resulted in an error.

DMA Setup FIS Interrupt

(DSS)

2 0b A DMA Setup FIS has been received with the ‘I’ bit set and

has been copied into system memory.

Set Device Bits Interrupt

(SDBS)

3 0b A Set Device Bits FIS has been received with the ‘I’ bit set

and has been copied into system memory.

Unknown FIS Interrupt

(UFS)

4 0b Read Only

When set to ‘1’, indicates that an unknown FIS was received

and has been copied into system memory. This bit is cleared

to ‘0’ by software clearing the PxSERR.DIAG.F bit to ‘0’.

Note that this bit does not directly reflect the PxSERR.DIAG.F

bit. PxSERR.DIAG.F is set immediately when an unknown

FIS is detected, whereas this bit is set when that FIS is

posted to memory. Software should wait to act on an

unknown FIS until this bit is set to ‘1’ or the two bits may

become out of sync.

Descriptor Processed

(DPS)

5 0b

A PRD with the ‘I’ bit set has transferred all of its data.

Port Connect Change

Status (PCS)

6 0b Read Only

1=Change in Current Connect Status. 0=No change in

Current Connect Status. This bit reflects the state of

PxSERR.DIAG.X. This bit is only cleared when

PxSERR.DIAG.X is cleared.

Device Mechanical

Presence Status (DMPS)

7 0b When set, indicates that a mechanical presence switch

attached to this port has been opened or closed, which may

lead to a change in the connection state of the device. This

bit is only valid if both CAP.SMPS and P0CMD.MPSP are set

to ‘1’.

Reserved 21:8 Reserved

PhyRdy Change Status

(PRCS)

22 0b Read Only

When set to ‘1’ indicates the internal PhyRdy signal changed

state. This bit reflects the state of P0SERR.DIAG.N. To

clear this bit, software must clear P0SERR.DIAG.N to ‘0’.

Incorrect Port Multiplier

Status (IPMS)

23 0b Indicates that the HBA received a FIS from a device whose

Port Multiplier field did not match what was expected. The

IPMS bit may be set during enumeration of devices on a Port

Multiplier due to the normal Port Multiplier enumeration

process. It is recommended that IPMS only be used after

enumeration is complete on the Port Multiplier.

Overflow Status (OFS) 24 0b Indicates that the HBA received more bytes from a device

than was specified in the PRD table for the command.

Reserved 25 Reserved

Interface Non-fatal Error

Status (INFS)

26 0b Indicates that the HBA encountered an error on the Serial

ATA interface but was able to continue operation.

Interface Fatal Error

Status (IFS)

27 0b Indicates that the HBA encountered an error on the Serial

ATA interface which caused the transfer to stop.