©2008 Advanced Micro Devices, Inc.

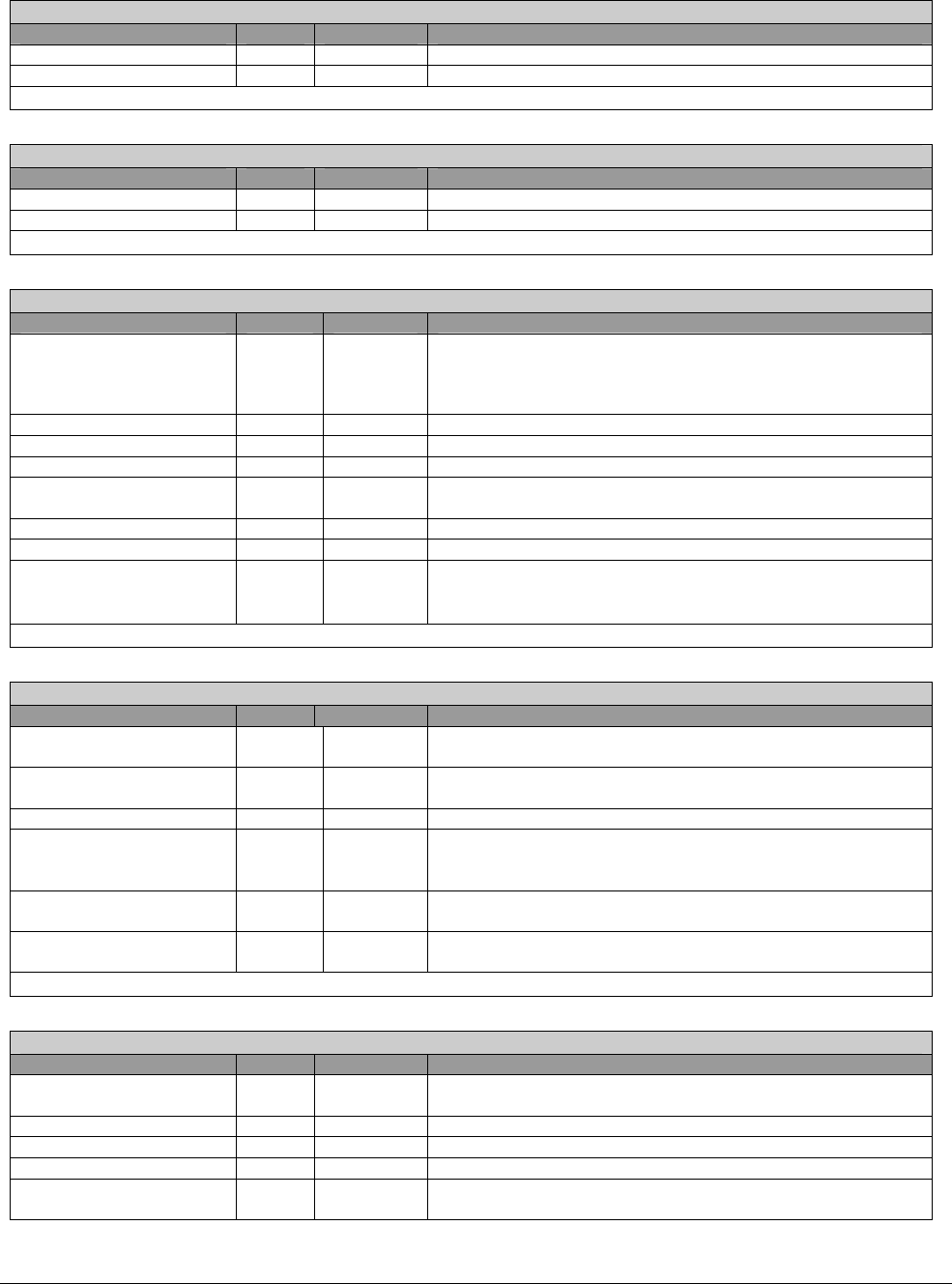

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 161

SwitchVoltageTime - RW – 8 bits - [PM_Reg: 63h]

Field Name Bits Default Description

SwitchVoltageTime 5:0 05h Programmable value (in 2us increment with 2us uncertainty)

Reserved 7:6 00b

SwitchVoltageTime register

SwitchGHI_Time - RW – 8 bits - [PM_Reg: 64h]

Field Name Bits Default Description

SwitchGhiTime 5:0 02h Programmable value (in 2us increment with 2us uncertainty)

Reserved 7:6 00b

SwitchGHITime register

UsbPMControl- RW – 8 bits - [PM_Reg: 65h]

Field Name Bits Default Description

UsbPhyS5PwrDwnEnable 0 0b Set to 1 to enable S4/S5 USB Phy power down support and to

disable S4 USB wakeup support.

The bit has to be clear to 0 (default) to support S4 USB

wakeup.

Reserved 1 0b

UsbResumeEnable 2 1b Set to 1 to enable S3 wakeup on USB device resume

Reserved 3 0b

UsbResetByPciRstEnable

4

1b Set to 1 to reset USB on the software (such as IO-64 or IO-

CF9 cycles) generated PCIRST#.

UsbS5ResetEnable 5 1b Set to 1 to enable USB reset on S4/S5 resume detection

Reserved 6 0b

SpecialFunc 7 0b If set to 1, S* -> S0 state transitions will use 1ms clock for

timing sequence; otherwise, 8µs clock will be used.

For K8 system, this bit must be cleared to use 8µs clock.

UsbPMControl register

MiscEnable66 - RW – 8 bits - [PM_Reg: 66h]

Field Name Bits Default Description

UsbBusyBreakEn

(available after A13)

0 0b

Setting this bit to 1 will cause C3/4 wakeup when USB OHCI

or EHCI DMA is active.

UsbOhciCstateMask

(available after A13)

1 0b

Setting this bit to 1 will prevent the system from entering C

state when USB OHCI DMA is active.

Reserved 4:2 000b

K8KbRstEn

5 0b

KB_RST# control for K8 system

0: Generate INIT#

1: Generate PCIRST#

UsbBusyBmStsEn

6

0b Setting this bit to 1 will cause C3/4 pop-up when USB OHCI or

EHCI DMA is active.

UsbOhciBmStsRdEn

(available after A13)

7 0b

Setting this bit to 1 will keep BM_STS read as 1 regardless of

BmStsRdMask when USB OHCI DMA is active.

MiscEnable66 register

MiscEnable67 – RW – 8 bits – [PM_Reg:67h]

Field Name Bits Default Description

CPU_STP_En

0 0b

CPU_STP# enable for C3 state in P4 system; no effect in K8

systems, for which CPU_STP# is always deasserted.

Slp_En 1 0b SLP# enable in C states

CC_En 2 0b C State enable; must be set in order to exercise C state

Reserved 3

BypassPwrGoodEn 4 0b If asserted, Southbridge will not wait for deassertion of

PWRGOOD to monitor for wakeup event