©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 129

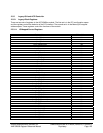

IntrCntrl1Reg2- RW – 8 bits - [IO_Reg: 21h]

Field Name Bits Default Description

IntrCntrl1Reg2 7:0 00h IRQ0 – IRQ7:

Read IMR

Write ICW2, ICW3, ICW4, OCW1

IntrCntrl1Reg2 register

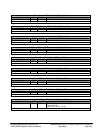

IMCR_Index- RW – 8 bits - [IO_Reg: 22h]

Field Name Bits Default Description

IMCR_Index 7:0 00h The IMCR is supported by two read/writeable IO ports 22/23h;

which are used as index and data port respectively. The

actual IMCR register is located at index 70h.

IMCR_Index register

IMCR_Data- RW – 8 bits - [IO_Reg: 23h]

Field Name Bits Default Description

IMCR_Data 7:0 00h The IMCR is supported by two read/writeable IO ports 22/23h;

which are used as index and data port respectively. The

actual IMCR register is located at index 70h and it is at bit 0.

The actual IMCR bit can only be accessed when bit port 22 is

set to 70h. Default value of IMCR is 0.

IMCR_Data register

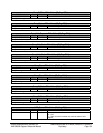

TimerCh0- RW – 8 bits - [IO_Reg: 40h]

Field Name Bits Default Description

TimerCh0 7:0 00h 8254 Timer 1 – Counter 0 Data Port

This timer is known as the System Clock timer and it is always

on. It is clocked internally by OSC/12 (1.19318MHz), and

asserts IRQ0 every time the timer rolls over. This timer is

used for time-of-day, diskette time-out, and other system

timing functions.

TimerCh0 register

TimerCh1- RW – 8 bits - [IO_Reg: 41h]

Field Name Bits Default Description

TimerCh1 7:0 00h 8254 Timer 1 – Counter 1 Data Port

This timer is normally used for ISA refresh cycles and is also

clocked by OSC/12 (1.19818MHz). Since this refresh function

is no longer needed (we don't have an external ISA bus), it

can be used as a general purpose timing function.

TimerCh1 register

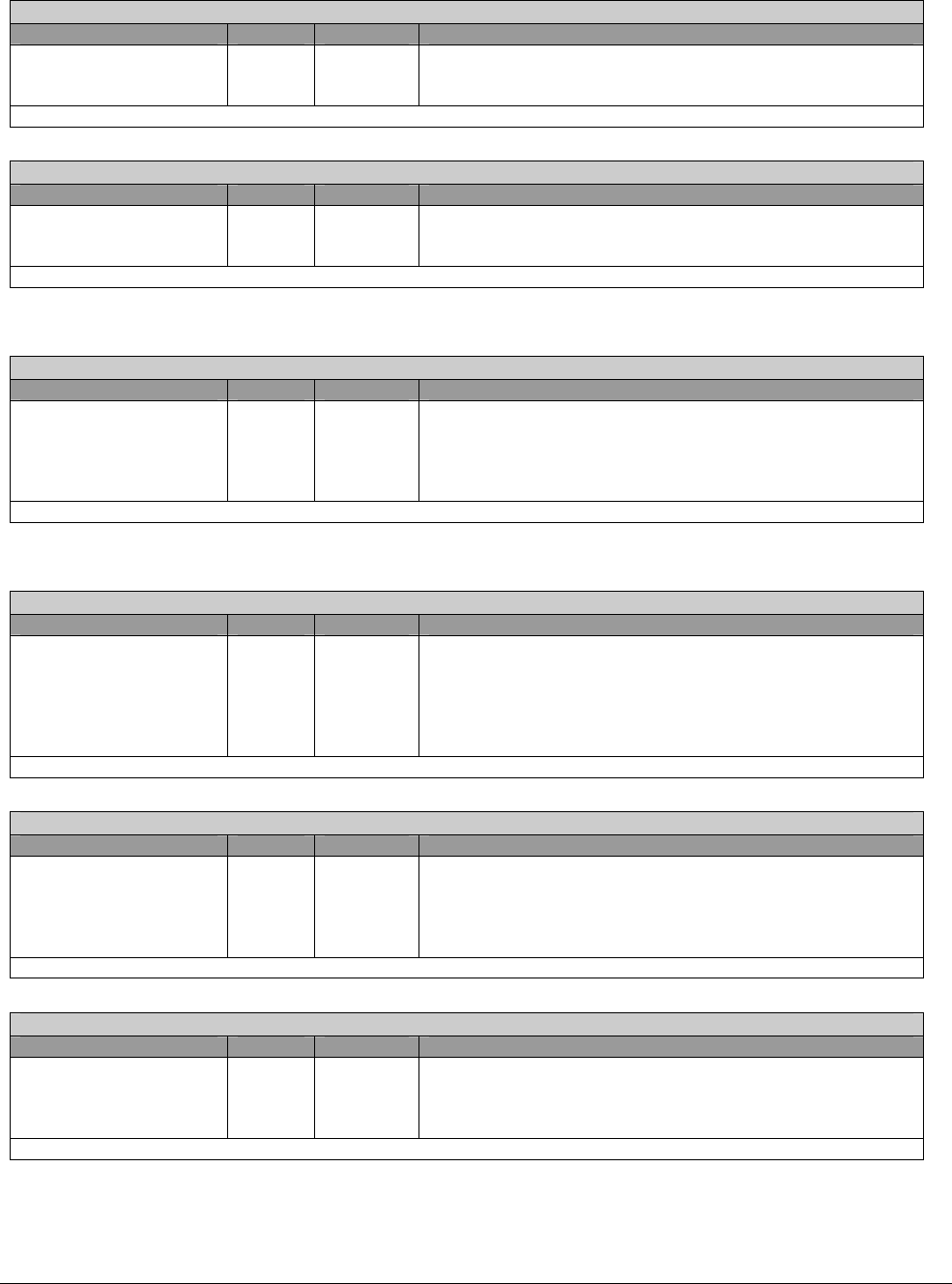

TimerCh2- RW – 8 bits - [IO_Reg: 42h]

Field Name Bits Default Description

TimerCh2 7:0 00h 8254 Timer 1 - Counter 2 Data Port

This is the speaker tone generator and is enabled by IO port

61H. It is clocked by OSC/12 (1.19318MHz) and directly

drives the output SPKR that goes to a speaker.

TimerCh2 register