©2008 Advanced Micro Devices, Inc.

IOXAPIC Registers

AMD SB600 Register Reference Manual Proprietary Page 297

4.5.2 Indirect Access Registers

Software needs to first select the register to access using the IO Register Select Register, and then read or

write using the IO Window Register.

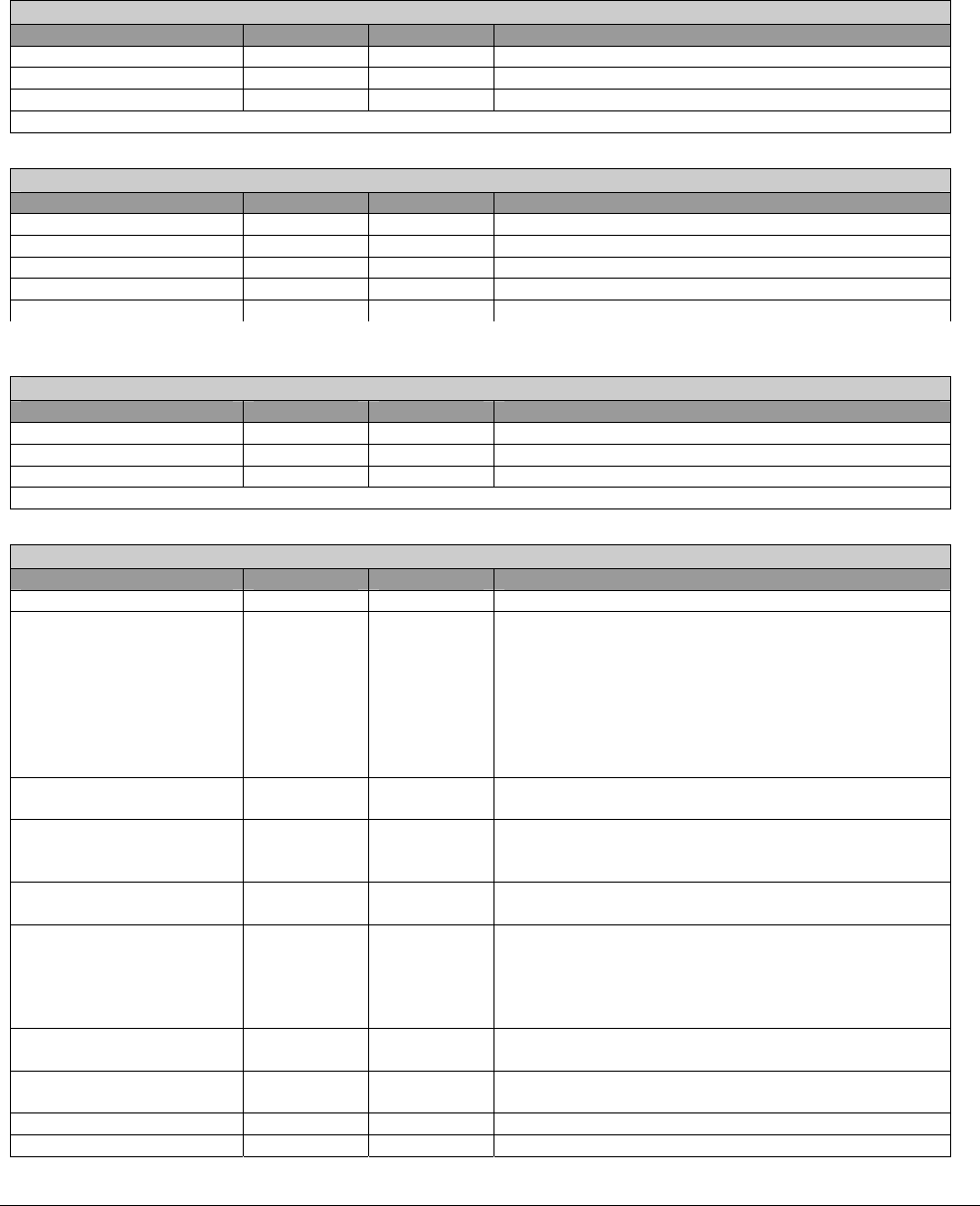

IOAPIC ID Register [Indirect Address Offset = 00H] RW

Field Name Bits Default Description

<reserved> 23:0 000000h

ID 27:24 0h IOAPIC device ID for APIC serial bus delivery mode

<reserved> 31:28 0h

Not used in XAPIC PCI bus delivery mode.

IOXAPIC Version Register [Indirect Address Offset = 01H] R

Field Name Bits Default Description

Version 7:0 21h PCI 2.2 compliant

<Reserved> 14:8 00h

PRQ 15 1b IRQ pin assertion supported

Max Redirection Entries 23:16 17h 24 entries [23:0]

<Reserved> 31:24 00h

IOAPIC Arbitration Register [Indirect Address Offset = 02H] R

Field Name Bits Default Description

<reserved> 23:0 000000h

Arbitration ID 27:24 0h Arbitration ID for APIC serial bus delivery mode

<reserved> 31:28 0h

Not used in XAPIC PCI bus delivery mode.

Redirection Table Entry [0–23] [Indirect Address Offset = 11/10H–3F/3EH] RW

Field Name Bits Default Description

Vector 7:0 00h Interrupt vector associated with this interrupt input

Delivery Mode 10:8 0h 000 – Fixed

001 – Lowest Priority

010 – SMI/PMI

011 – <reserved>

100 – NMI

101 – INIT

110 – <Reserved>

111 – ExtINT

Destination Mode 11 0b 0 – Physical

1 – Logical

Delivery Status 12 0b Read Only

0 – Idle

1 – Send Pending

Interrupt Pin Polarity 13 0b 0 – High

1 – Low

Remote IRR 14 0b Read Only.

Used for level triggered interrupts only.

Set when interrupt message delivered.

Cleared by EOI special cycle transaction or write to

EOI register

Trigger Mode 15 0b 0 – Edge

1 – Level

Mask 16 1b Mask the interrupt injection at the input of this device

Write 0 to unmask

Reserved 31:17 0000h

Reserved 55:32 000000h