©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 33

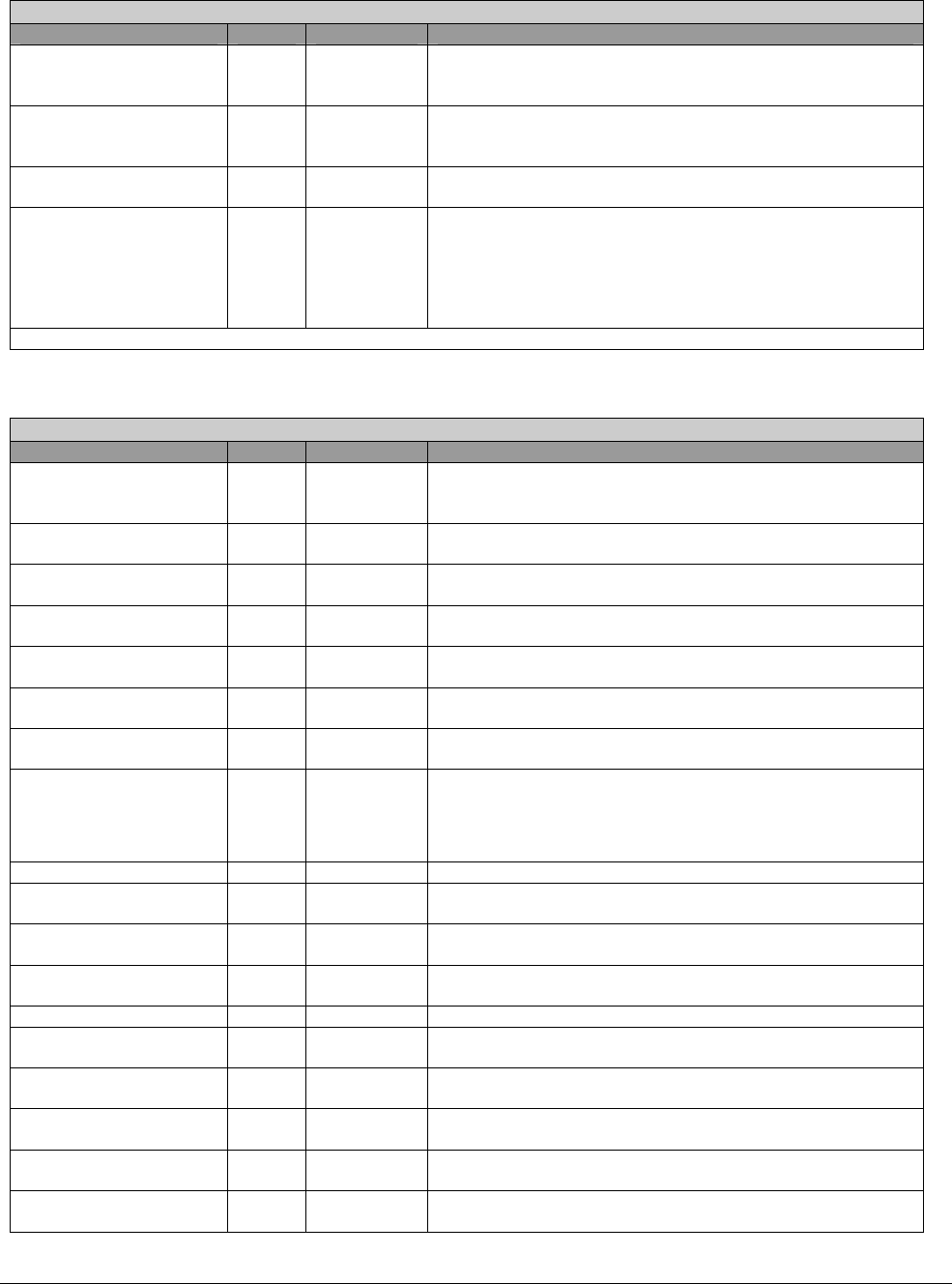

Port–N Interrupt Status - RW - 32 bits [Mem_reg: ABAR + port offset + 10h]

Field Name Bits Default Description

Host Bus Data Error

Status (HBDS)

28 0b Indicates that the HBA encountered a data error

(uncorrectable ECC / parity) when reading from or writing to

system memory.

Host Bus Fatal Error

Status (HBFS)

29 0b Indicates that the HBA encountered a host bus error that it

cannot recover from, such as a bad software pointer. In PCI,

such an indication would be a target or master abort.

Task File Error Status

(TFES)

30 0b This bit is set whenever the status register is updated by the

device and the error bit (bit 0) is set.

Cold Port Detect Status

(CPDS)

31 0b When set, a device status has changed as detected by the

cold presence detect logic. This bit can either be set due to a

non-connected port receiving a device, or a connected port

having its device removed. This bit is only valid if the port

supports cold presence detect as indicated by PxCMD.CPD

set to ‘1’.

Write 1 to clear these status bits.

Port-N Interrupt Enable - RW -32 bits [Mem_reg: ABAR + port offset + 14h]

Field Name Bits Default Description

Device to Host Register

FIS Interrupt Enable

(DHRE)

0 0b When set, GHC.IE is set, and P0IS.DHRS is set, the HBA

shall generate an interrupt.

PIO Setup FIS Interrupt

Enable (PSE)

1 0b When set, GHC.IE is set, and P0IS.PSS is set, the HBA shall

generate an interrupt.

DMA Setup FIS Interrupt

Enable (DSE)

2 0b When set, GHC.IE is set, and P0IS.DSS is set, the HBA shall

generate an interrupt.

Set Device Bits FIS

Interrupt Enable (SDBE)

3 0b When set, GHC.IE is set, and P0IS.SDBS is set, the HBA

shall generate an interrupt.

Unknown FIS Interrupt

Enable (UFE)

4 0b When set, GHC.IE is set, and P0IS.UFS is set to ‘1’, the HBA

shall generate an interrupt.

Descriptor Processed

Interrupt Enable (DPE)

5 0b When set, GHC.IE is set, and P0IS.DPS is set, the HBA shall

generate an interrupt.

Port Change Interrupt

Enable (PCE)

6 0b When set, GHC.IE is set, and P0IS.PCS is set, the HBA shall

generate an interrupt.

Device Mechanical

Presence Enable

(DMPE)

7 0b

When set, and GHC.IE is set to ‘1’, and P0IS.DMPS is set,

the HBA shall generate an interrupt.

For systems that do not support a mechanical presence

switch, this bit shall be a read-only ‘0’.

Reserved 21:8 Reserved

PhyRdy Change Interrupt

Enable (PRCE)

22 0b When set to ‘1’, and GHC.IE is set to ‘1’, and P0IS.PRCS is

set to ‘1’, the HBA shall generate an interrupt.

Incorrect Port Multiplier

Enable (IPME)

23 0b When set, and GHC.IE and P0IS.IPMS are set, the HBA shall

generate an interrupt.

Overflow Enable (OFE) 24 0b When set, and GHC.IE and P0IS.OFS are set, the HBA shall

generate an interrupt.

Reserved 25 Reserved

Interface Non-fatal Error

Enable (INFE)

26 0b When set, GHC.IE is set, and P0IS.INFS is set, the HBA shall

generate an interrupt.

Interface Fatal Error

Enable (IFE)

27 0b When set, GHC.IE is set, and P0IS.IFS is set, the HBA shall

generate an interrupt.

Host Bus Data Error

Enable (HBDE)

28 0b When set, GHC.IE is set, and P0IS.HBDS is set, the HBA

shall generate an interrupt.

Host Bus Fatal Error

Enable (HBFE)

29 0b When set, GHC.IE is set, and P0IS.HBFS is set, the HBA

shall generate an interrupt.

Task File Error Enable

(TFEE)

30 0b When set, GHC.IE is set, and P0S.TFES is set, the HBA shall

generate an interrupt.