©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 239

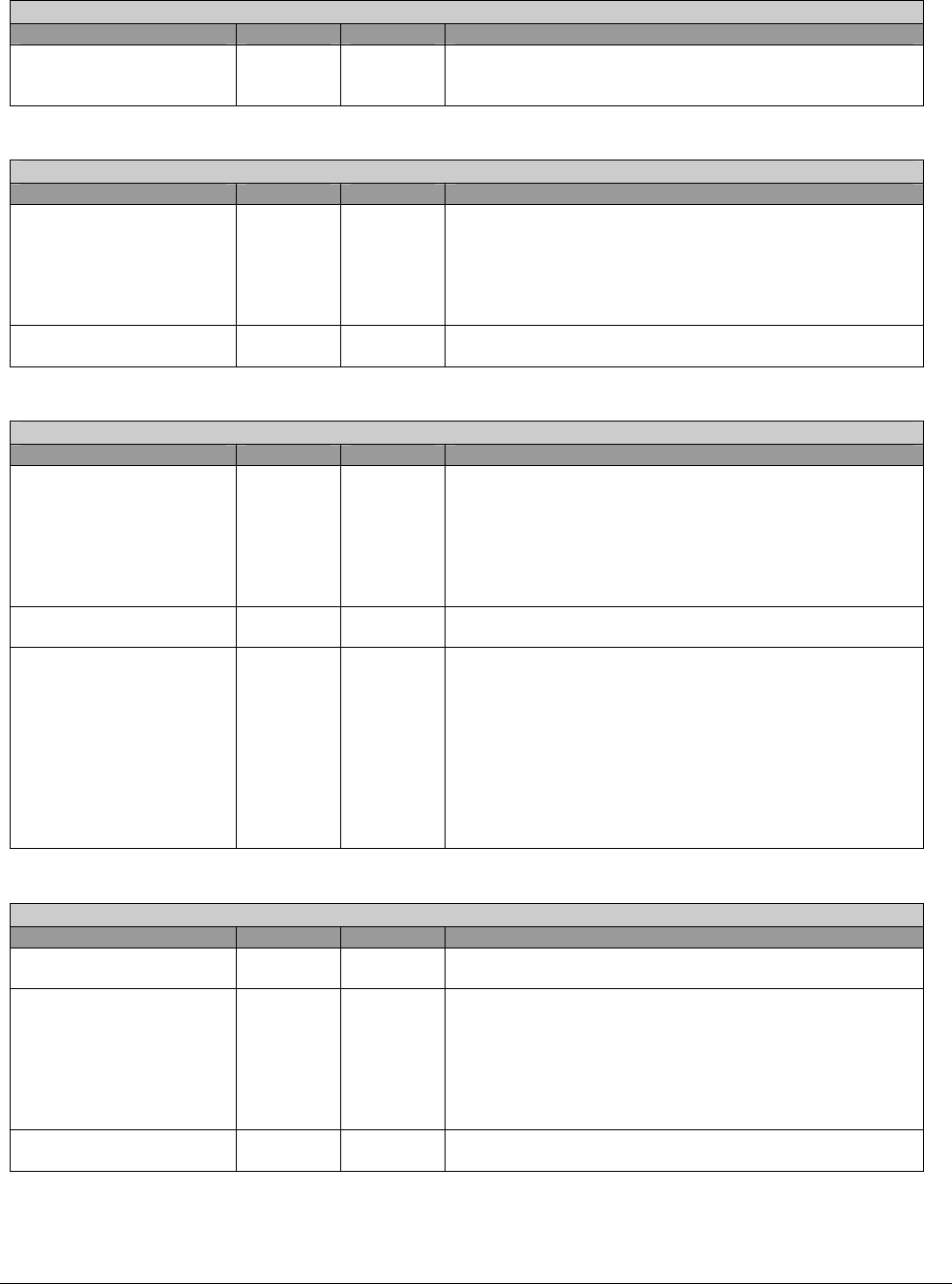

CORB Upper Base Address – RW – 32 bits – [Mem_Reg: Base + 44h]

Field Name Bits Default Description

CORB Upper Base

Address

31:0 00000000

h

Upper 32 bits address of the CORB. This register must not

be written when the DMA engine is running or the DMA

transfer may be corrupted.

CORB Write Pointer – RW – 16 bits – [Mem_Reg: Base + 48h]

Field Name Bits Default Description

CORB Write Pointer 7:0 00h Software writes the last valid CORB entry offset into this

field in dword granularity. The DMA engine fetches

commands from the CORB until the Read Pointer matches

the Write Pointer. This supports up to 256 CORB entries.

This field may not be written while the DMA engine is

running.

Reserved 15:8 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

CORB Read Pointer – RW – 16 bits – [Mem_Reg: Base + 4Ah]

Field Name Bits Default Description

CORB Read Pointer 7:0 00h Software reads this field to determine how many

commands it can write to the CORB without over-running.

The value read indicates the CORB Read Pointer offset in

dword granularity. The offset entry read from this field has

been successfully fetched by the DMA controller and may

be over-written by software. This field may be read while

the DMA engine is running.

Reserved 14:8 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.

CORB Read Pointer

Reset

15 0b Software writes a 1 to this bit to reset the CORB Read

Pointer to 0 and clear any residual prefetched commands

in the CORB hardware buffer within the controller. The

hardware will physically update this bit to 1 when the

CORB pointer reset is complete. Software must read a 1 to

verify that the reset completed correctly. Software must

clear this bit back to 0, by writing a 0, and then read back

the 0 to verify that the clear completed correctly. The

CORB DMA engine must be stopped prior to resetting the

Read Pointer or else DMA transfer may be corrupted.

CORB Control – RW – 8 bits – [Mem_Reg: Base + 4Ch]

Field Name Bits Default Description

CORB Memory Error

Interrupt Enable

0 0b If this bit is set, the controller will generate an interrupt if

the Memory Error Interrupt bit is set.

Enable CORB DMA

Engine

1 0b 0: DMA Stop

1: DMA Run

After software writes a “0” to this bit, the hardware may not

stop immediately. The hardware will physically update the

bit to “0” when the DMA engine is truly stopped. Software

must read a “0” from this bit to verify that the DMA engine

is truly stopped.

Reserved 7:2 00h Reserved. Software must do a read-modify-write to

preserve the value of these bits.