©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 115

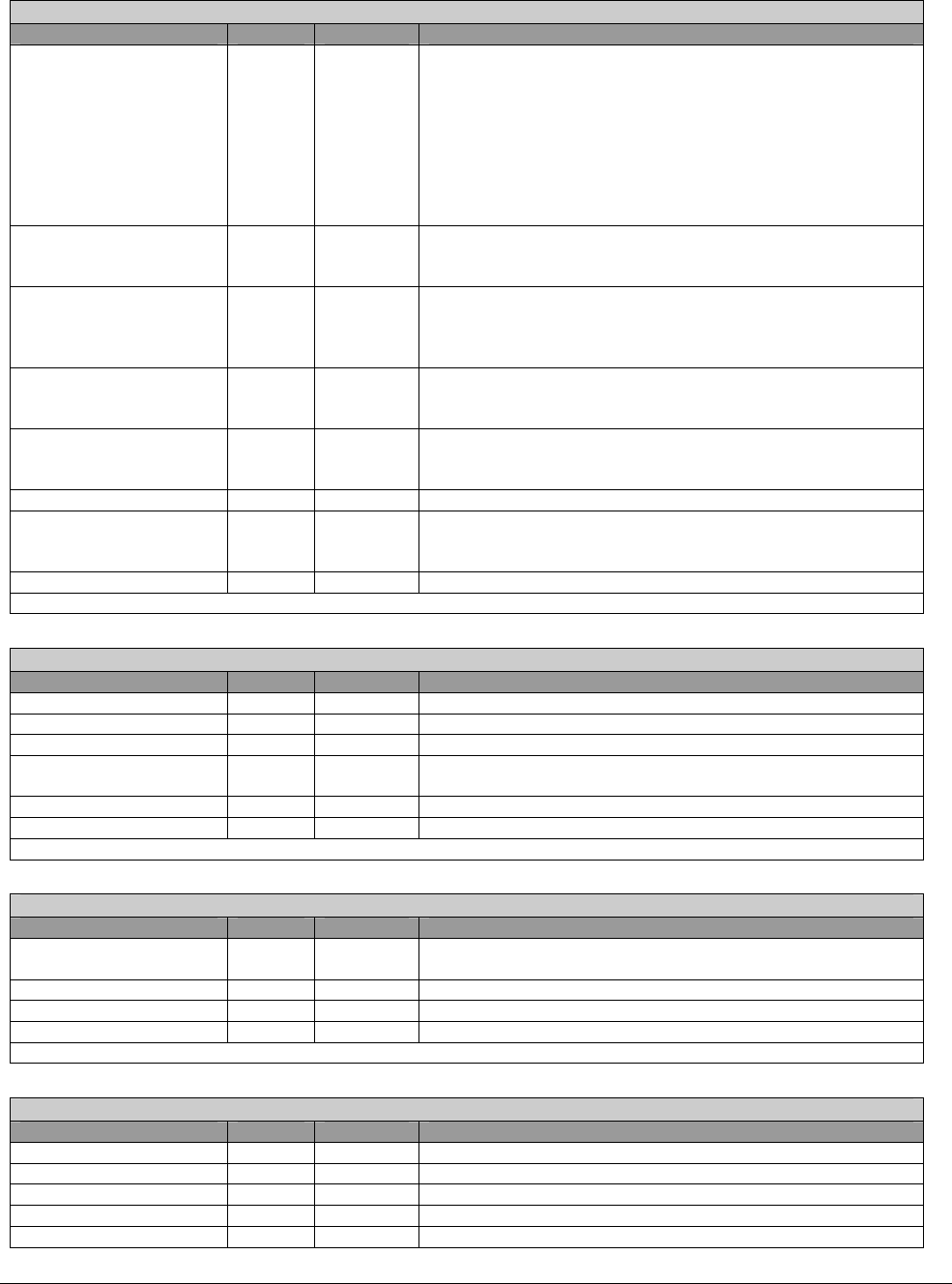

SATA_Cntrl - RW – 16 bits - [PCI_Reg: ACh]

Field Name Bits Default Description

ExtendIntrToWakeTime 18:16 000b This is used in K8 system to extend the interrupt break event

status. Whenever there is an apic interrupt, this logic will

extend the break event status by the amount of time defined

by this register. This is to avoid potential race condition

between CPU issuing the C1e command and the SB seeing

an interrupt. If CPU tries to enter C state before the extension

time expires, SB will break out from the C state. Each count

represents 2 microsecond increment and it has an uncertainty

of 2 microseconds.

DrqMaskEn 19 0b Setting this bit to 1 will cause the legacy DMA request to be

blocked if the DMA channel has not been initialized properly.

This bit is applicable to ASIC revision A21 and above.

IdeIrqFilterEn 20 0b Setting this bit to 1 will cause narrow pulses (less than several

A-link clocks wide) on the IDE IRQ line to be filtered out. This

means that no interrupt will be generated. This bit is applicable

to ASIC revision A21 and above.

TmrIrqEnhanceDisable 21 0b This bit should be set to 1 for the normal operation of the 8254

timer. This setting is required by ASIC revisions A11, A12, and

A13.

PIC_APIC_coexist 22 0b This bit should be set to 1 if PIC and APIC are to be enabled

at the same time in K8 system. There is no harm done even if

they don’t coexist at the same time.

Reserved 25:23 000b

SataIntMap 28:26 000b SATA interrupt mapping to PCI interrupt

000 - INTA#, 001 - INTB#, 010 - INTC#, 011 - INTD#, 100 -

INTE#, 101 - INTF#, 110 - INTG#, 111 - INTH#

Reserved 31:29 000b

SATA_Cntrl register

MSI Mapping Capability - R - 32 bits - [PCI_Reg: B0h]

Field Name Bits Default Description

Capability ID 7:0 08h This is a HyperTransport capability list item.

Capability Pointer 15:8 00h This is the end of capability list.

MsiEnable 16 0b MSI enable programmable through PCI_Reg: ADh bit 7

Fixed 17 1b The address for mapping MSIs is fixed at

0000_0000_FEEx_xxxxh.

Reserved 26:18 000h

Capability Type 31:27 10101b This is an MSI Mapping Capability block.

MSI Mapping Capability register

PciIntGpio - RW - 16 bits - [PCI_Reg: BCh]

Field Name Bits Default Description

PciIntGpioOut 3:0 0h Output data for each PCI INT# GPIO providing bits [7:4] and

[15:12] are enabled

PciIntGpioEnB 7:4 Fh Output enable for each PCI INT# GPIO (active low)

PciIntGpioStatus 11:8 - Input status for each PCI INT# GPIO [Read Only]

PciIntIsGpio 15:12 0h Set to 1 to use PCI interrupt INTH/G/F/E# as GPIO

PciIntGpio register

UsbIntMap - RW - 16 bits - [PCI_Reg: BEh]

Field Name Bits Default Description

UsbInt1Map 2:0 000b (OHCI0) UsbInt1 interrupt mapping to PCI interrupt

UsbInt2Map 5:3 001b (OHCI1 & OHCI3) UsbInt2 interrupt mapping to PCI interrupt

Reserved 7:6 00b

UsbInt3Map 10:8 010b (OHCI2 & OHCI4) UsbInt3 interrupt mapping to PCI interrupt

UsbInt4Map 13:11 011b (EHCI) UsbInt4 interrupt mapping to PCI interrupt