©2008 Advanced Micro Devices, Inc.

SATA Registers (Device 18, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 43

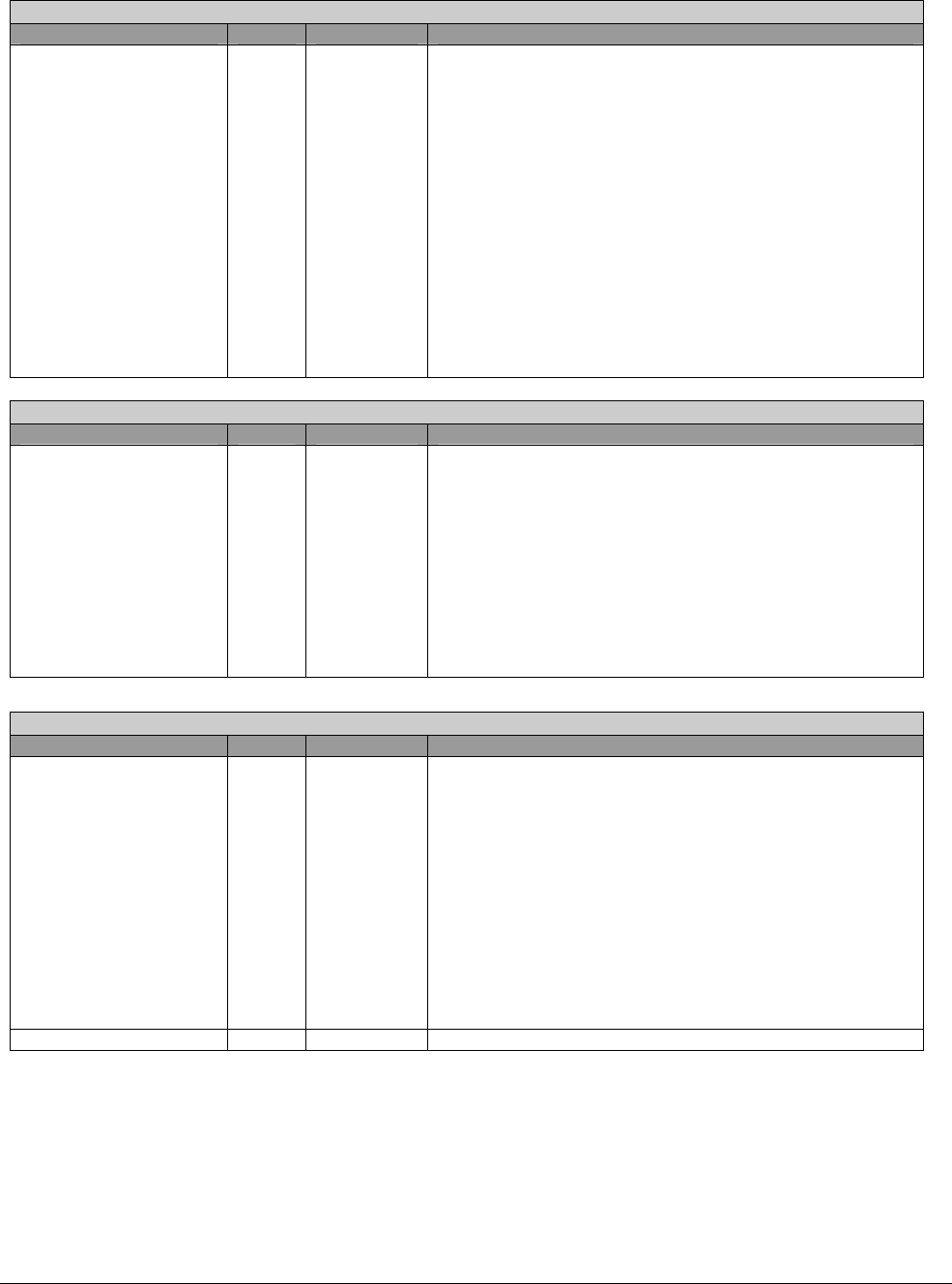

Port-N Serial ATA Active – RW – 32 bits [Mem_reg: ABAR + port offset + 34h]

Field Name Bits Default Description

Device Status (DS) 31:0 00000000h

This field is bit significant. Each bit corresponds to the TAG

and command slot of a native queued command, where bit 0

corresponds to TAG 0 and command slot 0. This field is set

by software prior to issuing a native queued command for a

particular command slot. Prior to writing PxCI[TAG] to ‘1’,

software will set DS[TAG] to ‘1’ to indicate that a command

with that TAG is outstanding. The device clears bits in this

field by sending a Set Device Bits FIS to the host. The HBA

clears bits in this field that are set to ‘1’ in the SActive field of

the Set Device Bits FIS. The HBA only clears bits that

correspond to native queued commands that have completed

successfully.

Software should only write this field when PxCMD.ST is set to

‘1’. This field is cleared when PxCMD.ST is written from a ‘1’

to a ‘0’ by software. This field is not cleared by a

COMRESET or a software reset.

Port-N Command Issue – RW – 32 bits [Mem_reg: ABAR + port offset + 38h]

Field Name Bits Default Description

Commands Issued (CI) 31:0 00000000h

This field is bit significant. Each bit corresponds to a

command slot, where bit 0 corresponds to command slot 0.

This field is set by software to indicate to the HBA that a

command has been built in system memory for a command

slot and may be sent to the device. When the HBA receives

a FIS which clears the BSY, DRQ, and ERR bits for the

command, it clears the corresponding bit in this register for

that command slot. Bits in this field shall only be set to ‘1’ by

software when PxCMD.ST is set to ‘1’.

This field is also cleared when PxCMD.ST is written from a ‘1’

to a ‘0’ by software.

Port- N SNotification – RWC – 32 bits [Mem_reg: ABAR + port offset + 3Ch]

Field Name Bits Default Description

PM Notify (PMN)

15:0 0000h This field indicates whether a particular device with the

corresponding PM Port number issued a Set Device Bits FIS

to the host with the Notification bit set.

PM Port 0h sets bit 0

…

PM Port Fh sets bit 15

Individual bits are cleared by software writing 1’s to the

corresponding bit positions.

This field is reset to default on a HBA Reset, but it is not reset

by COMRESET or software reset.

Reserved 31:16 Reserved