©2008 Advanced Micro Devices, Inc.

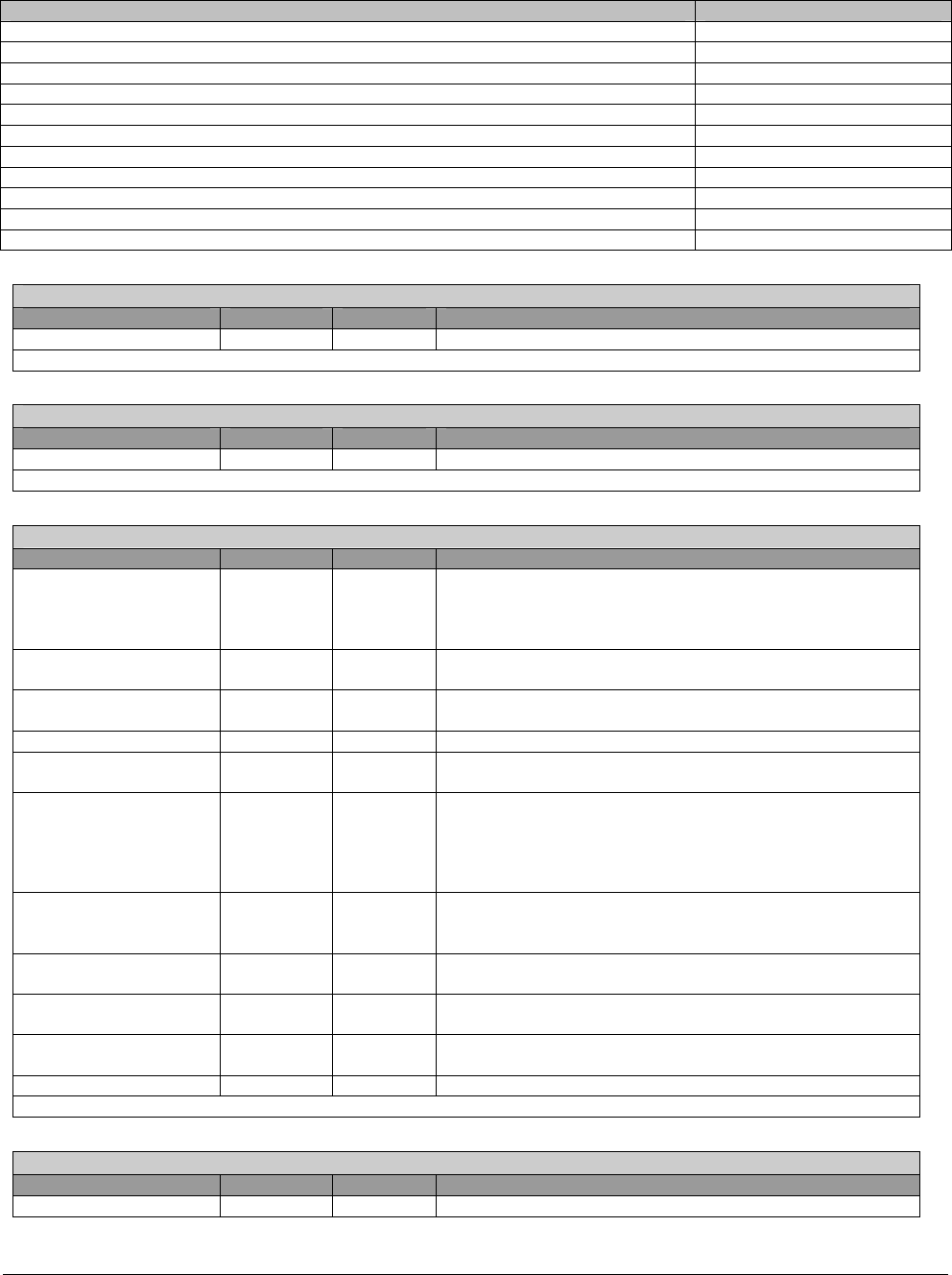

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 266

Register Name Offset Address

Additional Priority 49h

PCICLK Enable Bits 4Ah

Misc Control 4Bh

AutoClockRun Control 4Ch

Dual Address Cycle Enable and PCIB_SCLK_Stop Override 50h

MSI Mapping Capability 54h

Signature Register for Microsoft Rework for Subtractive Decode 58h

Prefetch Timeout Limit 5Ch

SPCI IDSEL MaskB 5Eh

Prefetch Size Control 60h

Misc Control 64h

Vender ID - R - 16 bits - [PCI_Reg: 00h]

Field Name Bits Default Description

VID 15:0 1002h Vendor ID

Vendor ID register

Device ID - R - 16 bits - [PCI_Reg: 02h]

Field Name Bits Default Description

DID 15:0 4384h Device ID

Device ID register

Command - RW - 16 bits - [PCI_Reg: 04h]

Field Name Bits Default Description

IO Enable 0 0b IO response enable,

0: Disabled,

1: Enabled,

PCIB responses IO space accesses on primary bus.

Memory Enable 1 0b Memory response enable, ‘0’ disabled, ‘1’ enabled, PCIB

responses memory space accesses on primary bus.

Master Enable 2 0b Master enable, ‘0’ disabled, ‘1’ enabled, the ability of PCIB

to act as a PCI bus master on primary bus.

Special Enable 3 0b Hardwired to 0 to indicate that PCIB ignores special cycles.

Mem Invalidate 4 0b Hardwired to 0 to indicate that PCIB doesn’t issue memory

write and invalidate command by itself.

VGA Snoop Enable 5 0b VGA snoop enable, when ‘0’ VGA palette write transactions

on the primary interface are ignored unless it falls into

PCIB’s IO address range. When ‘1’ VGA palette write

transactions are positively decoded and forwarded

downstream.

Parity Error Enable 6 0b Parity Error Response, ‘0’ disables PCIB to assert

P_SERR# and P_PERR# or report Detected Parity Error to

the status register, ‘1’ enables PCIB.

Addr Stepping Enable 7 0b Controls whether or not to do address/data stepping, PCIB

doesn’t. Read Only

System Error Enable 8 0b SERR# enable, ‘0’ disables PCIB to assert P_SERR# and

report Signaled System Error bit, ‘1’ enables PCIB.

Fast Back-to-Back

Enable

9 0b Hardwired to 0 to indicate that PCIB is not capable of

issuing fast back-to-back transactions on the primary bus.

Reserved 15:10 00h Reserved

PCI Command register

Status- RW - 16 bits - [PCI_Reg: 06h]

Field Name Bits Default Description

Reserved 3:0 0h Reserved