©2008 Advanced Micro Devices, Inc.

LPC ISA Bridge (Device 20, Function 3)

AMD SB600 Register Reference Manual Proprietary Page 249

3 Register Descriptions: PCI Bridges

3.1 LPC ISA Bridge (Device 20, Function 3)

Note: Some LPC functions are controlled by, and associated with, certain PCI configuration registers in the

SMBus/ACPI device. For more information refer to section 2.3: SMBus Module and ACPI Block (Device 20,

Function 0). The diagram below lists these LPC functions and the associated registers.

LPC

LPC Controller Enable

LPC Drive strength control

C0h

64h --

PCI_Reg:

3.1.1 Programming Interface

• Write LPC_enable bit in function 0, register 64, bit 20.

• Enable LPC address decode ranges.

• Program DMA controller for any bus master or DMA cycles.

• Perform LPC cycles from PCI or DMA requests from LPC agent.

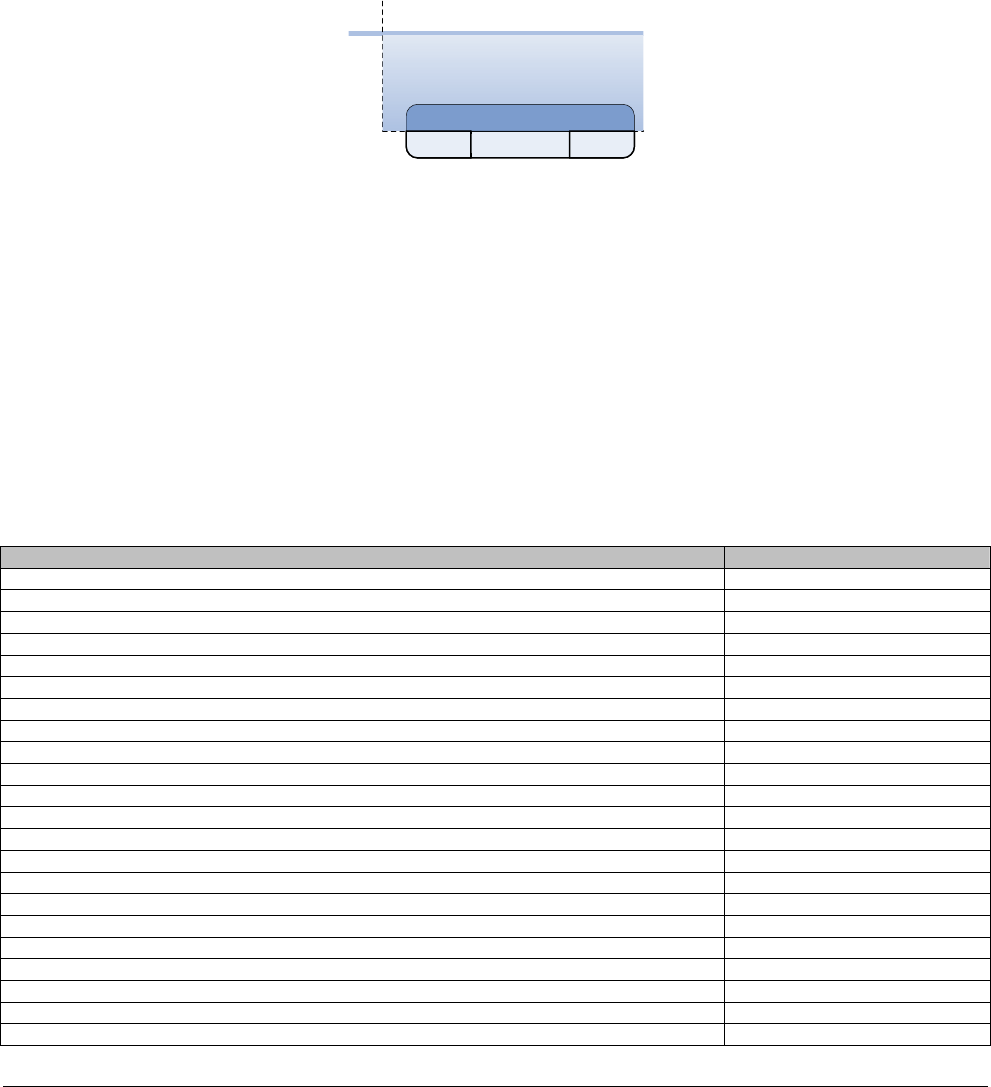

3.1.2 PCI Configuration Registers

The LPC host controller supports a set of configuration register required by the PCI specification.

Registers not listed here will have this default behavior: read from the register returns 0’s; write to the

register is ignored.

Register Name Offset Address

VID 00h

DID 02h

CMD 04h

STATUS 06h

Revision ID/Class Code 08h

Cache Line Size 0Ch

Latency Timer 0Dh

Header Type 0Eh

BIST 0Fh

Base Address Reg 0 10h

Subsystem ID & Subsystem Vendor ID 2Ch

Capabilities Pointer 34h

PCI Control 40h

IO Port Decode Enable Register 1 44h

IO Port Decode Enable Register 2 45h

IO Port Decode Enable Register 3 46h

IO Port Decode Enable Register 4 47h

IO/Mem Port Decode Enable Register 5 48h

LPC Sync Timeout Count 49h

IO/Mem Port Decode Enable Register 6 4Ah

Memory Range Register 4Ch

Rom Protect 0 50h