©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 145

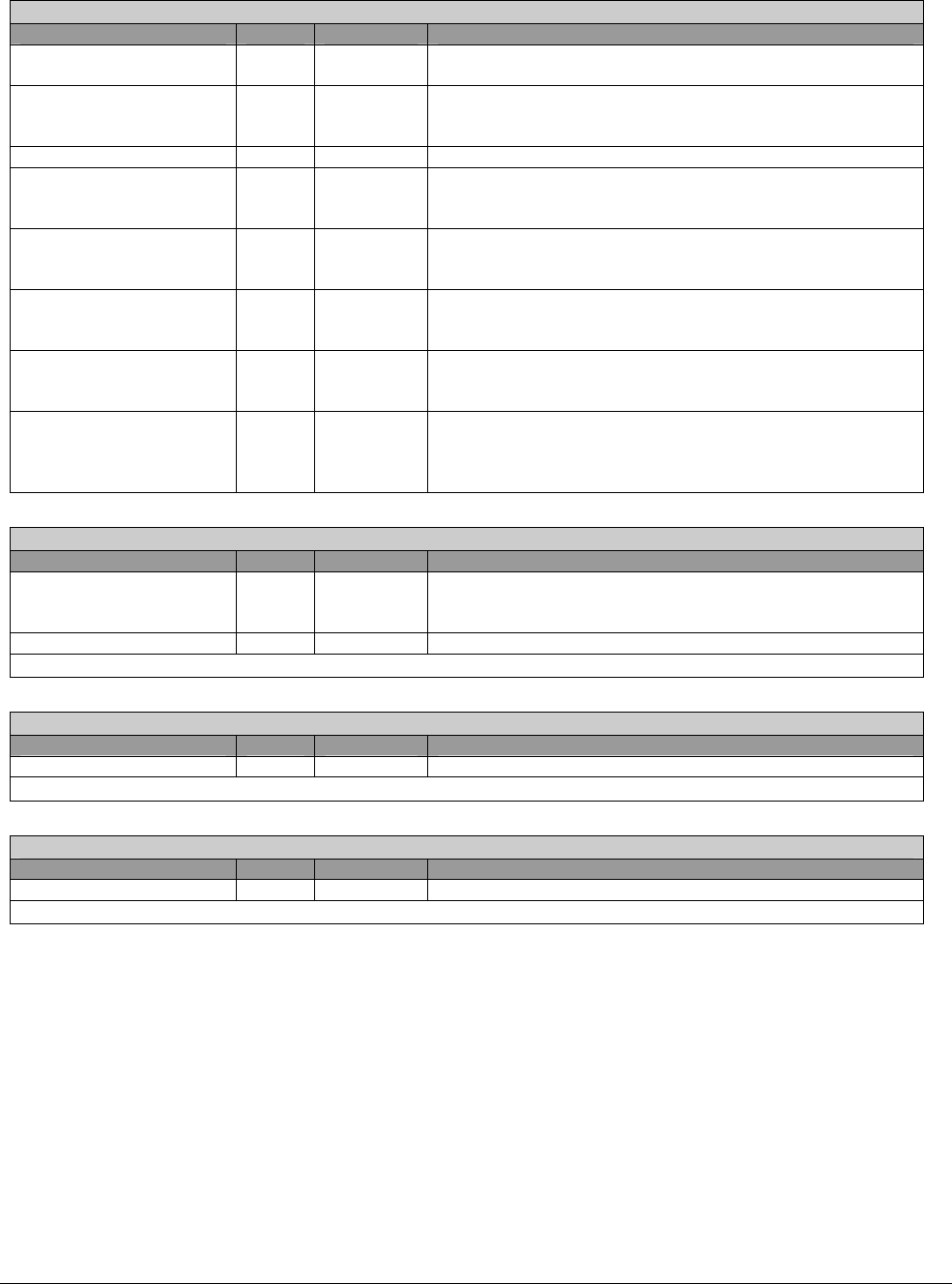

AcpiEn - RW – 8 bits - [PM_Reg: 10h]

Field Name Bits Default Description

EOSEnale 0 0b Set 1 by software and clear by hardware. This bit needs to

be set in order to generate SMI#/SCI

RTC_En_En 1 0b RTC_EN enable bit. When this bit is set, RTC_EN

(AcpiPmEvtBlk, index x02, bit 10) is visible; otherwise, it is

always 0

Reserved 2 0b

TMR_En_En 3 0b TMR_EN enable bit. When this bit is set, TM_EN

(AcpiPmEvtBlk, index x02, bit 0) is visible; otherwise, it is

always 0

LEVENT_EN_EN 4 0b LEVENT_EN enable bit. When this bit is set, LEVENT_EN

(AcpiGpe0Blk, index x04, bit 8) is visible; otherwise, it is

always 0

GBL_EN_EN 5 0b GBL_EN enable bit. When this bit set, GBL_EN

(AcpiPmEvtBlk, index x02, bit 5) is visible; otherwise, it is

always 0

PciExpWakeDisEn 6 0b PciExpWakeDis enable bit. When this bit is set,

PciExpWakeDis (AcpiPmEvtBlk, index x02, bit 14) is visible;

otherwise, it is always 1

GpioToGEventSel 7 0b This bit is applicable to ASIC Revision A12 and above.

0: ACPI_EVENT[30] register is routed to use GPIO2 as input

1: ACPI_EVENT[30] register is routed to use GPIO66 as

input

S1AgpStpEn - RW – 8 bits - [PM_Reg: 11h]

Field Name Bits Default Description

S1AgpStpEn 0 0b AgpStp enable in S1 state

1: Enable

0: Disable

Reserved 7:1 00h

S1AgpStpEn register.

PmTmr2InitValue - RW – 8 bits - [PM_Reg: 12h]

Field Name Bits Default Description

PmTmr2InitValue 7:0 00h PmTmr2 load value

PmTmr2InitValue register.

PmTmr2CurValue - R – 8 bits - [PM_Reg: 13h]

Field Name Bits Default Description

PmTmr2CurValue 7:0 -- PmTmr2 current value

PmTmr2CurValue register.