©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 269

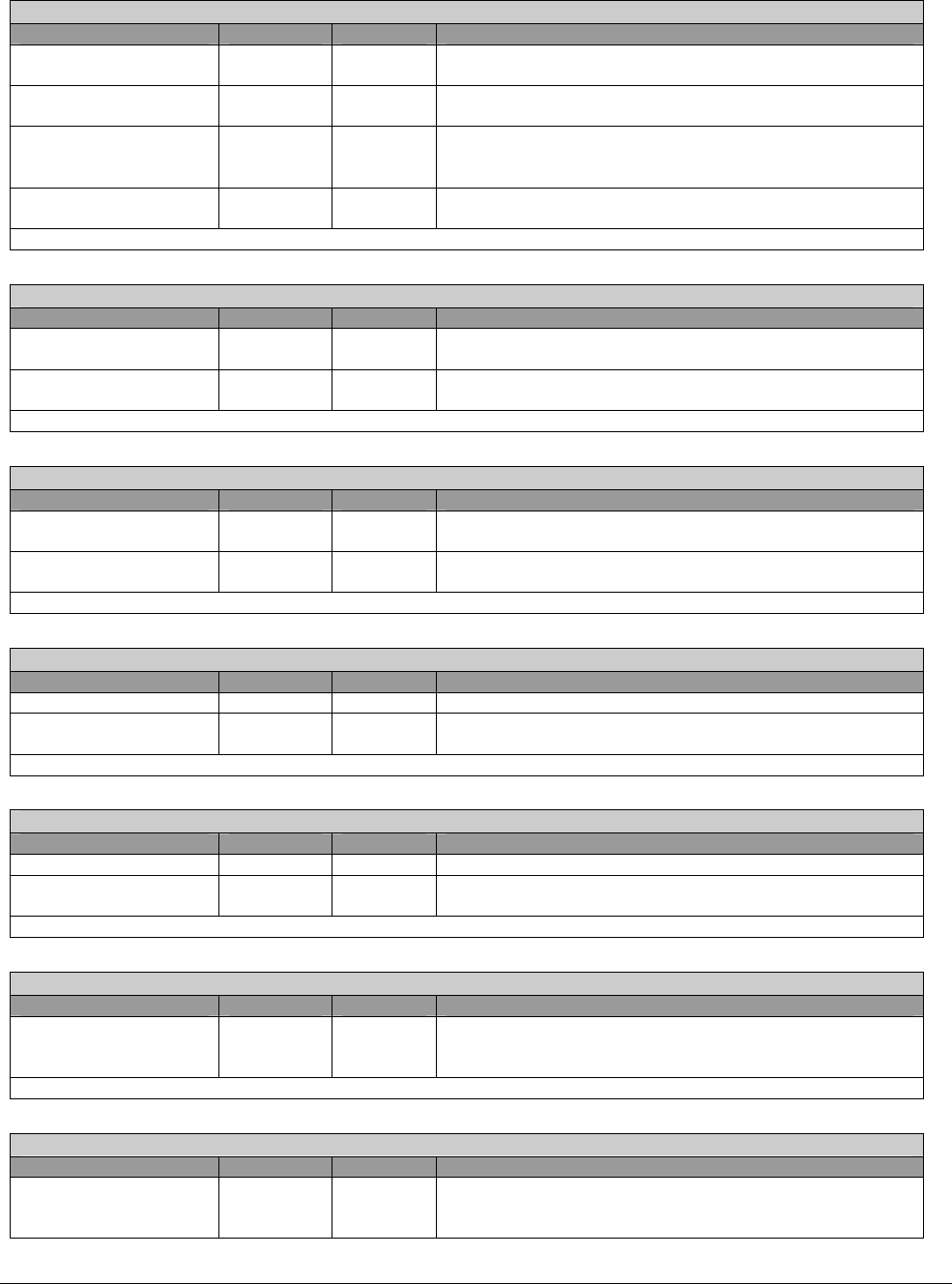

Secondary Status- RW - 16 bits - [PCI_Reg: 1Eh]

Field Name Bits Default Description

Received Secondary

Target Abort

12 0b Received Target Abort on the secondary bus, write clears it.

Received Secondary

Master Abort

13 0b Received Master Abort on the secondary bus, write clears it.

Received Serr 14 0b Received System Error on the secondary bus, PCIB asserts

P_SERR# to propagate the error back to the primary bus,

write clears it.

Data Parity Error 15 0b Detected Parity Error on the secondary bus, PCIB detected

a parity error and will assert S_PERR#, write clears it.

Secondary status register

Memory Base- RW - 16 bits - [PCI_Reg: 20h]

Field Name Bits Default Description

Reserved 3:0 0h Indicates a non-prefetchable 32-bit memory space. Read

Only

Non Pref Mem Base 15:4 000h Defines the highest 12 bits ([31:20]) of the base address of

this 32-bit memory space.

Memory base register

Memory Limit- RW - 16 bits - [PCI_Reg: 22h]

Field Name Bits Default Description

Reserved 3:0 0h Indicates a non-prefetchable 32-bit memory space. Read

Only.

Non Pref Mem Limit 15:4 000h Defines the highest 12 bits ([31:20]) of the upper limit of this

32-bit memory space.

Memory limit register

Prefetchable Memory Base- RW - 16 bits - [PCI_Reg: 24h]

Field Name Bits Default Description

Reserved 3:0 0h Indicates a 32-bit only +memory space. Read Only

Pref Mem Base 15:4 000h Defines the highest 12 bits ([31:20]) of the base address of

this 32-bit memory space.

Prefetchable memory base register

Prefetchable Memory Limit- RW - 16 bits - [PCI_Reg: 26h]

Field Name Bits Default Description

Reserved 3:0 0h Indicates a 32-bit only memory space. Read Only.

Perf Mem Limit 15:4 000h Defines the highest 12 bits ([31:20]) of the upper limit of this

32-bit memory space.

Prefetchable memory limit register

IO Base Upper 16 Bits- RW - 16 bits - [PCI_Reg: 30h]

Field Name Bits Default Description

IOBase Upper 15:0 0000h Top 16 bits of the base address of 32-bit IO transactions.

If the IO address decode mode bit (Regx48 bit[29] ) is clear

then these bits will be zero

IO base upper 16 bits

IO Limit Upper 16 bits- RW - 16 bits - [PCI_Reg: 32h]

Field Name Bits Default Description

IOLimit Upper 15:0 0000h Top 16 bits of the upper limit of 32-bit IO transactions.

If the IO address decode mode bit (Regx48 bit[29] ) is clear

then these bits will be zero