©2008 Advanced Micro Devices, Inc.

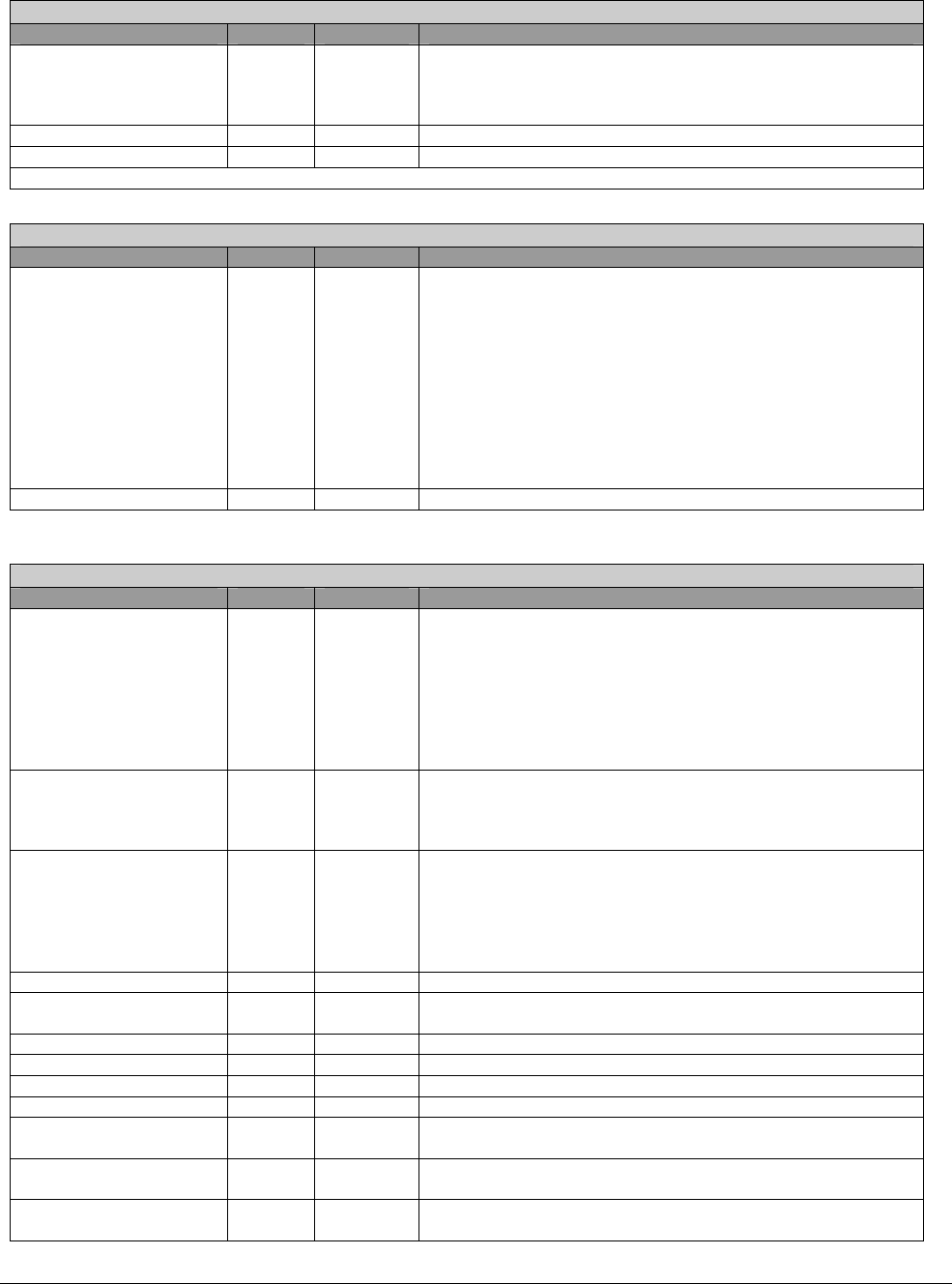

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 107

MiscEnable- RW - 8 bits - [PCI_Reg: 62h]

Field Name Bits Default Description

USB_Fast_SMI_Disable 5 0b For K8 system, legacy USB can request SMI# to be sent out

early before IO completion. Some applications may have

problem with this feature. BIOS should set this bit to 1 to

disable the feature.

Reserved 6 0b

IDE_GPIO_Enable 7 0b If this bit is set to 1, the IDE bus is configured as GPIO

MiscEnable register

AzIntMap- RW - 8 bits - [PCI_Reg: 63h]

Field Name Bits Default Description

AzIntMap 2:0 110b Interrupt routing table for HD Audio. Setting this register

routes the HD audio’s interrupt to the specific PCI interrupt

before it is routed to the interrupt controller

000 – INTA#

001 – INTB#

010 – INTC#

011 – INTD#

100 – INTE#

101 – INTF#

110 – INTG#

111 – INTH#

Reserved 7:3 00000b

Features Enable- RW - 32 bits - [PCI_Reg: 64h]

Field Name Bits Default Description

PIC_Enable

0 1b PIC (8259) Programmable Interrupt Controller enable

0 - I/O cycles to master PIC:20,21, slave PIC:a0, a1, ELCR

registers 4D0, 4D1h, and the PCI interrupt Mapping Registers

(C00, C01), and Numberic Coprocessor Error Register

(IRQ13) (0F0h) are not accepted.

1 - (default) I/O cycles to APIC are not decoded but I/O cycles

to these above addresses will be positive decoded on PCI and

run to the internal 8259 PIC

Timer_Enable 1 1b 0 – I/O cycles to timers/counter (040-043h) will not be claimed

on ISA

1 – I/O cycles to timers/counter will be claimed on ISA and run

to the internal 8254 Timer/Counter

PMIO_Register Enable

2 1b Power management enable register

0 – I/O cycles to Power management registers (CD6 and

CD7h) will not be claimed

1 – I/O cycles to Power management registers will be claimed

and run to the internal Power Management logic (BIOS should

always set it to 1)

Ioapic_enable 3 0b When set, this block will decode ioapic address

CheckOwnReq 4 0b If set, the SB600 will check its own REQ# as the PCI_ACTIVE

signal in addition to BMREQ#

BmReqEn 5 0b BMREQ# enable

Reserved 6 0b

XIOAPIC_ENA 7 1b XIOAPIC enable; this bit is only valid if bit 3 is set.

GEVENT5_ENA 8 0b BIOS should always set this bit to 1 to enable GEVENT5.

Ext_KBRST_EnB 9 0b Enable external KB_RST# input. When set to 0, GEVENT[1]

is used as KBRST# input

MultiMediaTimerIrqEn 10 0b High Precision Event Timer (also called Multimedia Timer)

interrupt enable

Ext_A20En 11 0b Enable external Ga20In input. When set to 1, GEVENT[0] is

used as Ga20In input