©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 202

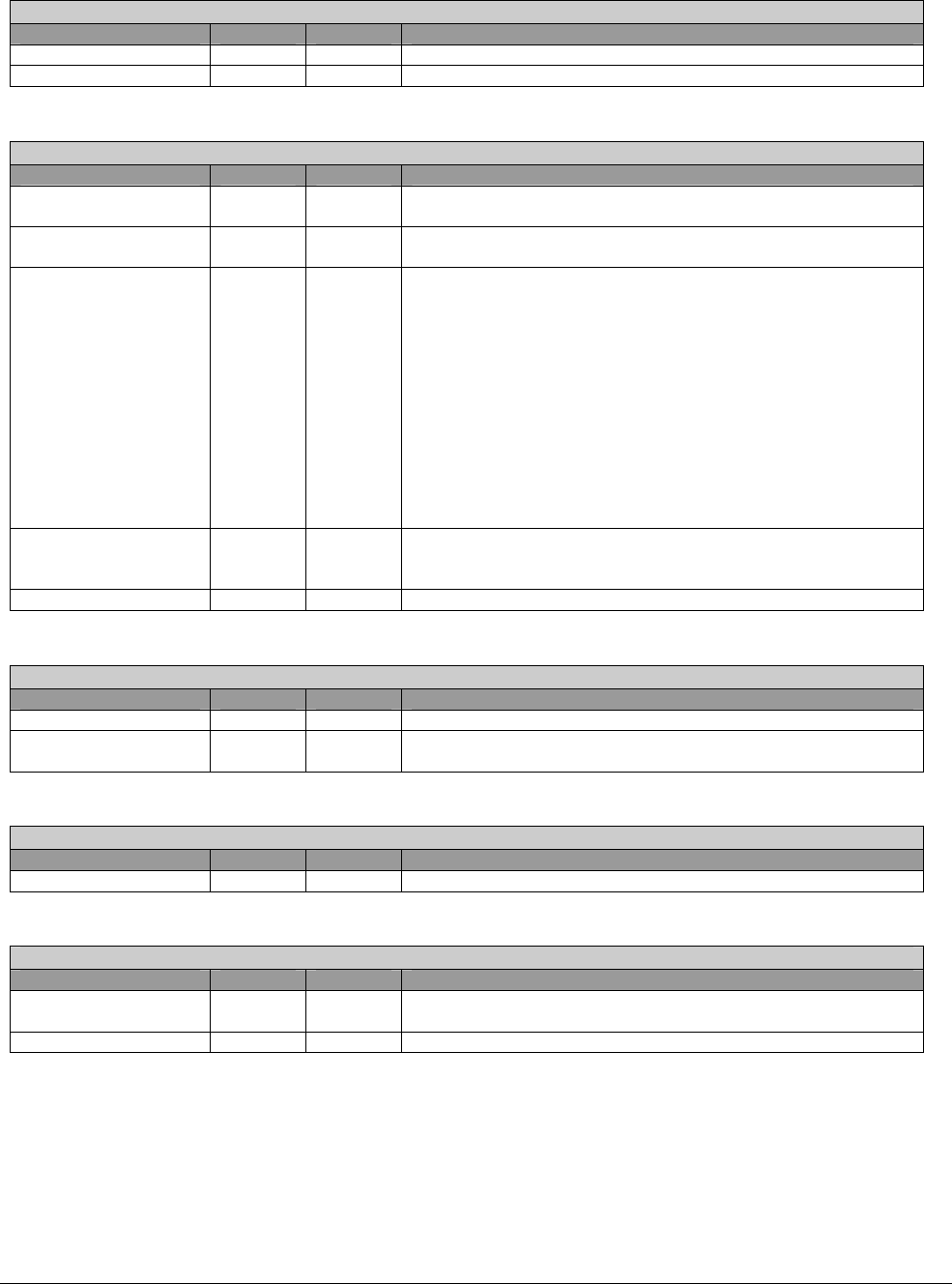

MSI Capability Register Set IDs- R – 16 bits – [PCI_Reg: 40h]

Field Name Bits Default Description

Capability ID 7:0 05h Read only. 05h indicates it is an MSI capability register set.

Pointer to Next ID 15:8 00h Read only. 00h indicates there is no additional register set.

MSI Message Control Register- RW – 16 bits – [PCI_Reg: 42h]

Field Name Bits Default Description

MSI Enable 0 0b 0 - Function Is disabled from using MSI.

1 - Function is enabled to use MSI.

Multiple Message

Capable

3:1 0h Hardwired to 0 to indicate the device would like 1 message

allocated to it.

Multiple Message

Enable

6:4 0h Read/Write. Software programs a 3-bit value into this field

indicating the actual number of messages allocated to the

device. The number allocated can be equal or less than the

number actually requested. The field is encoded as follows:

Value Number of Messages Requested

000b 1

001b 2

010b 4

011b 8

100b 16

101b 32

110b reserved

111b reserved

64-bit Address

Capable

7 0b Hardwired to 0 to indicates that function does not implement the

upper 32 bits of the Message Address register and is incapable

of generating a 64-bit memory address.

Reserved 15:8 00h

MSI Message Address Register- RW – 32 bits – [PCI_Reg: 44h]

Field Name Bits Default Description

Reserved 1:0 Reserved.

MSI Address 31:2 0000_00

00h

Lower 32 bits of the system specified message address always

DW aligned.

MSI Message Data Register- RW – 16 bits – [PCI_Reg: 48h]

Field Name Bits Default Description

MSI Data 15:0 0h System-specified message.

MSI Program Weight- RW – 8 bits – [PCI_Reg: 4Ch]

Field Name Bits Default Description

Program Weight 5:0 04h This register specifies the programmable priority of audio

device’s message signaled interrupt request.

Reserved 7:6 0h