©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 52

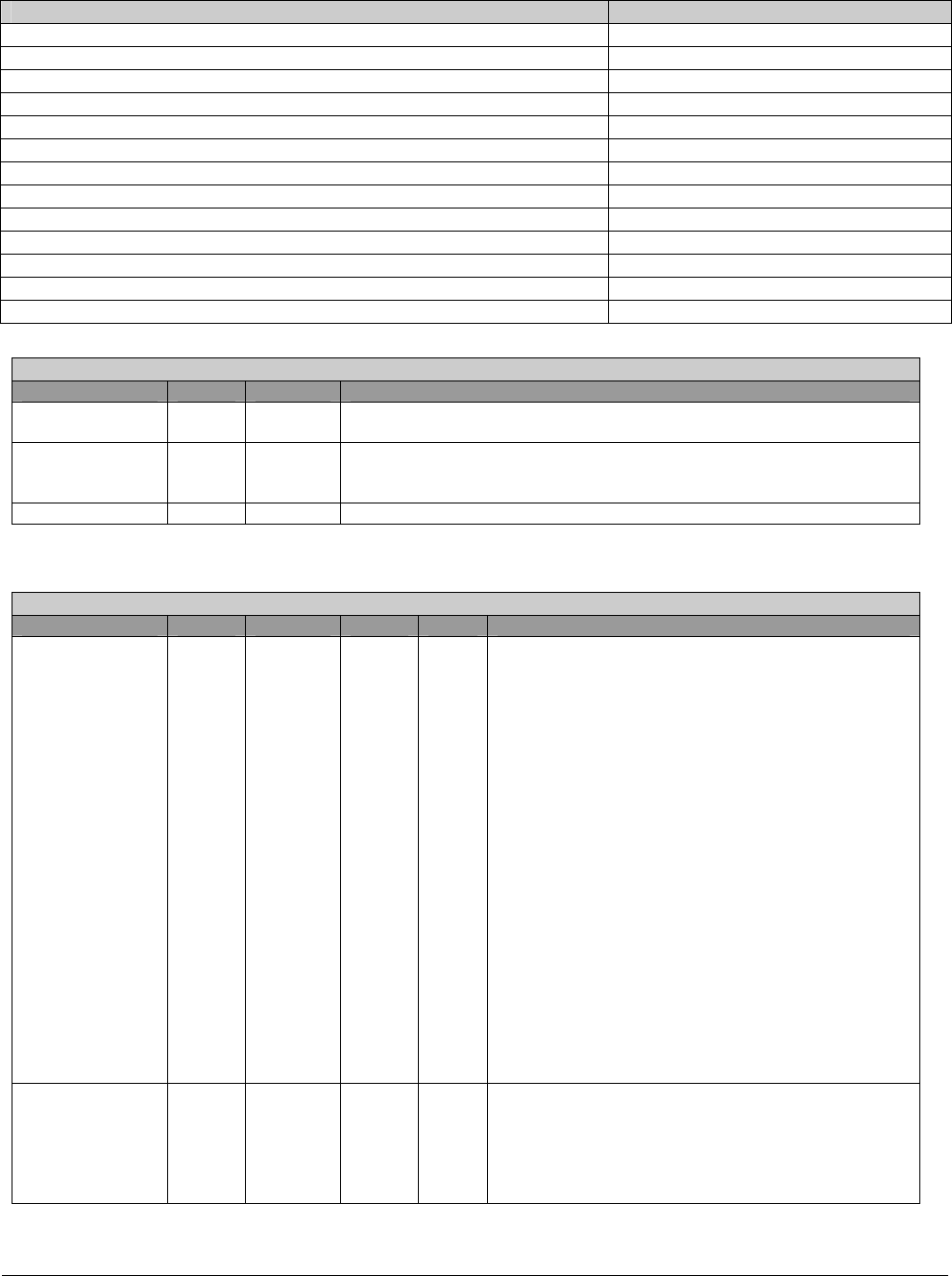

Register Name Offset Address

HcBulkCurrentED 2Ch

HcDoneHead 30h

HcFmInterval 34h

HcFmRemaining 38h

HcFmNumber 3Ch

HcPeriodicStart 40h

HcLSThreshold 44h

HcRhDescriptorA 48h

HcRhDescriptorB 4Ch

HCRhStatus 50h

HcRhPortStatus[1] 54h

… …

HcRhPortStatus[NDP] 54+4*NDP

HcRevision – R - 32 bits - [MEM_Reg : 00h]

Field Name Bits Default Description

REV 7:0 10h

Revision.

This read-only field contains the version of HCI specification.

L 8 1b

Legacy

This read-only field is 1, indicating that the legacy support registers are

present in this HC.

Reserved 31:9 Reserved

HcControl - 32 bits - [MEM_Reg : 04h]

Field Name Bits Default HCD HC Description

CBSR 1:0 00b RW R

ControlBulkServiceRatio

This specifies the service ratio between Control and

Bulk Eds. Before processing any of the non-periodic

lists, HC must compare the ratio specified with its

internal count on how many nonempty Control Eds

have been processed, in determining whether to

continue serving another Control ED or switching to

Bulk Eds.

CBSR

No. of Control Eds Over Bulk Eds Served

0

1:1

1

2:1

2

3:1

3

4:1

PLE 2 0b RW R

PeriodicListEnable

This bit is set to enable the processing of the periodic

list in the next Frame. If cleared by HCD, processing

of the periodic list does not occur after the next SOF.

HC must check this bit before it starts processing the

list.