©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 155

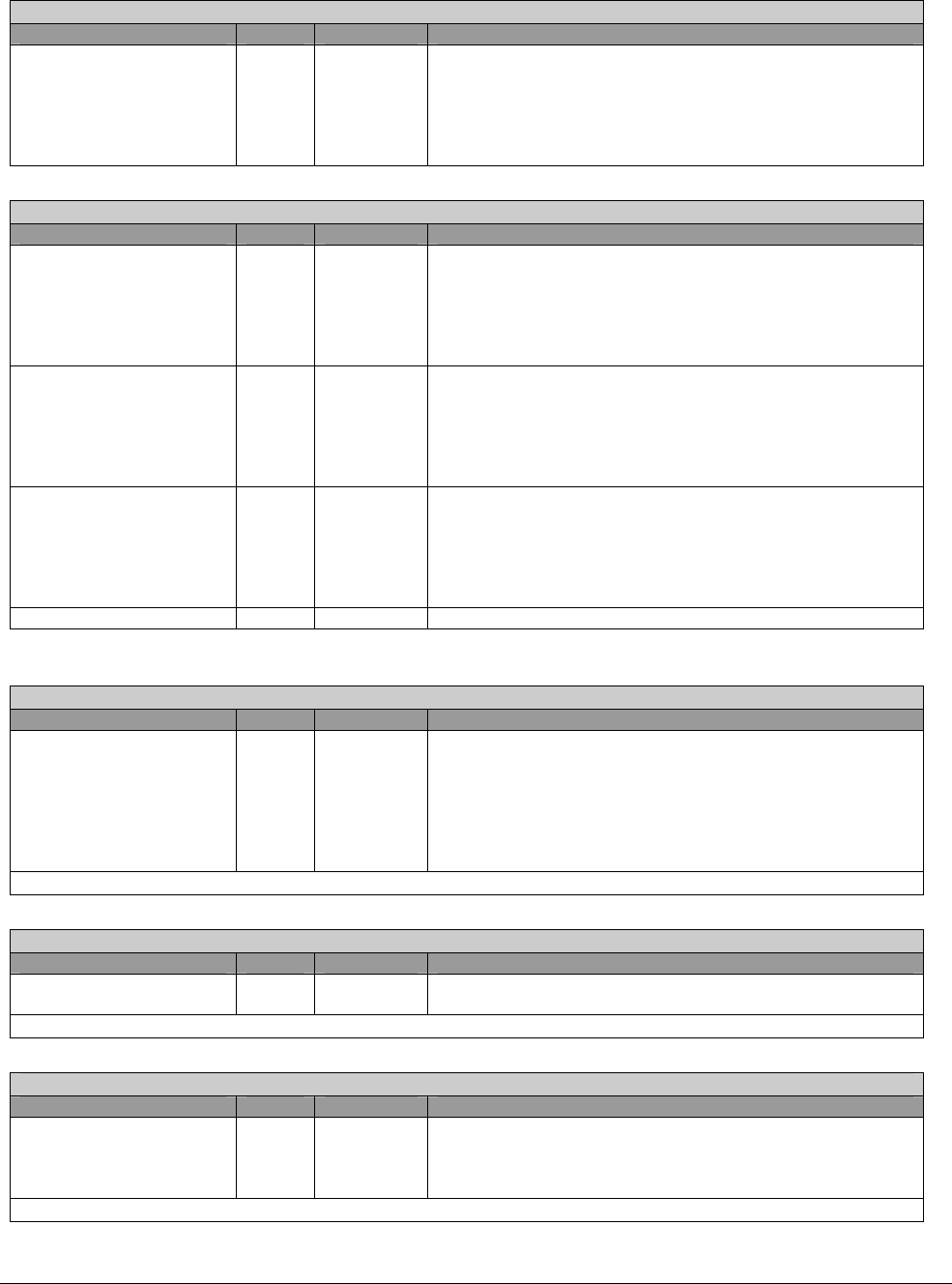

OthersConfig- RW – 8 bits - [PM_Reg: 3Ch]

Field Name Bits Default Description

Ac97Config 7:6 00b These two bits configure AC97 PME

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 Ac97 PME to generate SMI#

10 Ac97 PME to generate SMI# followed by SCI

11 Ac97 PME to generate IRQ13

MorePmeConfig – RW – 8 bits - [PM_Reg: 3Dh]

Fi/eld Name Bits Default Description

OtherThermConfig 1:0 00b These two bits configure OtherTherm

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 OtherTherm to generate SMI#

10 OtherTherm to generate SMI# followed by SCI

11 OtherTherm to generate IRQ13

Gpm9Config 3:2 00b These two bits configure GPM[9]

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 GPM[9] to generate SMI#

10 GPM[9] to generate SMI# followed by SCI

11 GPM[9] to generate IRQ13

PCIeHotPlugConfig 5:4 00b These two bits configure PCIeHotPlug

00 ACPI Event (trigger SCIOUT or SMI#

depending on SCI_EN bit)

01 PCIeHotPlug to generate SMI#

10 PCIeHotPlug to generate SMI# followed by SCI

11 PCIeHotPlug to generate IRQ13

Reserved 7:6 00b

VRT_T1 - RW – 8 bits - [PM_Reg: 3Eh]

Field Name Bits Default Description

VRT_T1 7:0 01h The RTC battery is sampled (to conserve power) periodically

to checks its state of health. VRT_T1 and VRT_T2 make up

the interval of the checking. When VRT_Enable is high, the

battery is being sampled. When VRT_enable is low, the

battery is not being sampled. This register defines the time

of VRT enable being high for RTC battery monitor circuit, in

miliseconds.

VRT_T1 register.

VRT_T2 - RW – 8 bits - [PM_Reg: 3Fh]

Field Name Bits Default Description

VRT_T2 7:0 FFh This register defines the time of VRT enable being low for the

RTC battery monitor circuit, in 4 ms increment.

VRT_T2 register.

AD_Pull_UpB - RW – 8 bits - [PM_Reg: 40h]

Field Name Bits Default Description

AD_Pull_UpB 7:0 00h This register controls integrated pull-up for AD[31:24]

respectively.

0: Enable

1: Disable

AD_Pull_UpB register.