©2008 Advanced Micro Devices, Inc.

AC ’97 Controller Functional Descriptions

AMD SB600 Register Reference Manual Proprietary Page 225

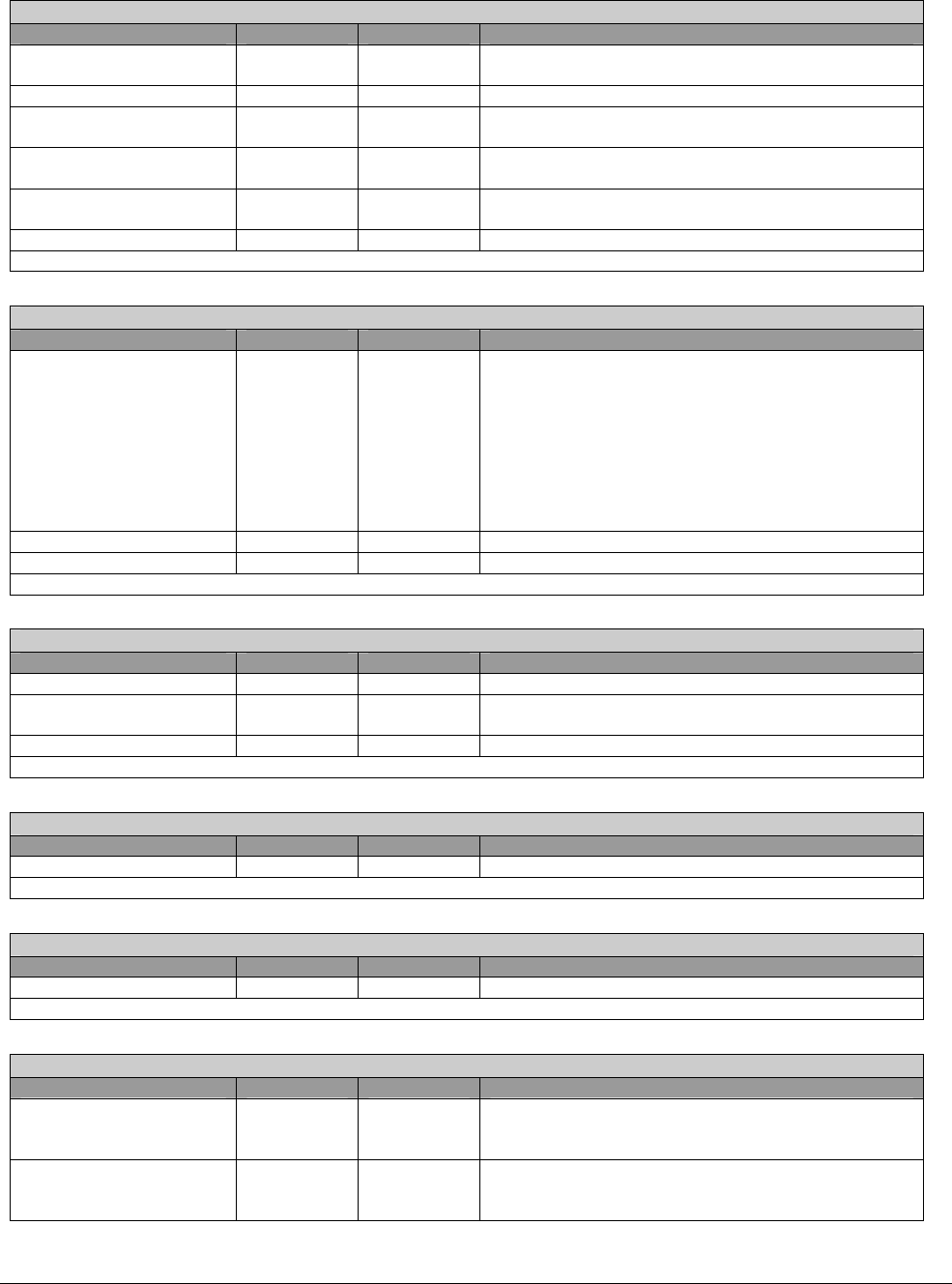

Output DMA 1/2/3 FIFO Info– R - 32 bits - [MEM_Reg: 70h]

Field Name Bits Default Description

out DMA3 Used 14:10 00h Number of filled FIFO entries of Output DMA3 (FIFO

size 6).

Reserved 15 0b

out DMA1 Free 20:16 00h Number of free FIFO entries of Output DMA1 (FIFO

size 6).

out DMA2 Free 25:21 00h Number of free FIFO entries of Output DMA2 (FIFO

size 6).

out DMA3 Free 30:26 00h Number of free FIFO entries of Output DMA3 (FIFO

size 6).

Reserved 31 0b

Output DMA1/2/3 FIFO Used/Free Register:

GPIO Out Data– RW - 32 bits - [MEM_Reg: 74h]

Field Name Bits Default Description

Gpio Out Data en 0 0b Enables the sending of GPIO data on the next frame’s

slot 12. Data comes from bit[20:1] of this register. This

bit has higher priority than reg0x08[22]. That means if

both this bit and reg0x08[22] are set, then GPIO data

comes from bit[20:1] of this register, not from DMA3.

Writing 1 to this bit enables this data to be sent out.

After some time, when data is sent out, this bit

automatically goes back to 0. Bit[20:1] can be written

only when this bit is 0.

Gpio Out Data 20:1 000h Gpio Out Data

Reserved 31:21 000h

Gpio Out Data Register: Data to the modem.

Input GPIO Data– R - 32 bits - [MEM_Reg: 78h]

Field Name Bits Default Description

Input Gpio data 19:0 00000h Input Gpio(modem) data from AC'97 Codecs (ORed)

Input Gpio Codec ID 22:20 0h ID of Codec who send the Gpio data (001 - Master,

010- Slave1, 100 - Slave2)

Reserved 31:23 00h

Input Gpio data Register: Data from the modem.

Modem Mirror– RW - 32 bits - [MEM_Reg: 7Ch]

Field Name Bits Default Description

Modem mirror 31:0 0000_0000h Data written by modem for communication with Audio.

Modem mirror Register.

Audio Mirror– R - 32 bits - [MEM_Reg: 80h]

Field Name Bits Default Description

Audio mirror 31:0 0000_0000h Data written by audio for communication with modem.

Audio mirror Register.

Modem Fifo Flush– W - 32 bits - [MEM_Reg: 88h]

Field Name Bits Default Description

Output DMA1 Fifo Flush 0 0b Writing to this bit flushes modem output DMA1 fifo,

i.e., the indexes and Used/Free counts are reset.

Reading this bit returns 0.

Output DMA2 Fifo Flush 1 0b Writing to this bit flushes modem output DMA2 fifo,

i.e., the indexes and Used/Free counts are reset.

Reading this bit returns 0.