©2008 Advanced Micro Devices, Inc.

HD Audio Controllers Registers

AMD SB600 Register Reference Manual Proprietary Page 248

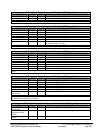

Stream Descriptor BDL Pointer Lower Base Address – RW – 32 bits

Input Stream 0 - [Mem_Reg: Base + 98h]

Input Stream 1 - [Mem_Reg: Base + B8h]

Input Stream 2 - [Mem_Reg: Base + D8h]

Input Stream 3 - [Mem_Reg: Base + F8h]

Output Stream 0 - [Mem_Reg: Base + 138h]

Output Stream 2 - [Mem_Reg: Base + 158h]

Output Stream 3 - [Mem_Reg: Base + 178h]

Field Name Bits Default Description

Reserved 6:0 00h Hardwired to 0’s to force 128 byte alignment of the BDL.

Buffer Descriptor List

Lower Base Address

31:7 0000000h Upper 25 bits of the lower 32 bit address of the Buffer

Descriptor List. This value should not be modified except

when the Run bit is “0”.

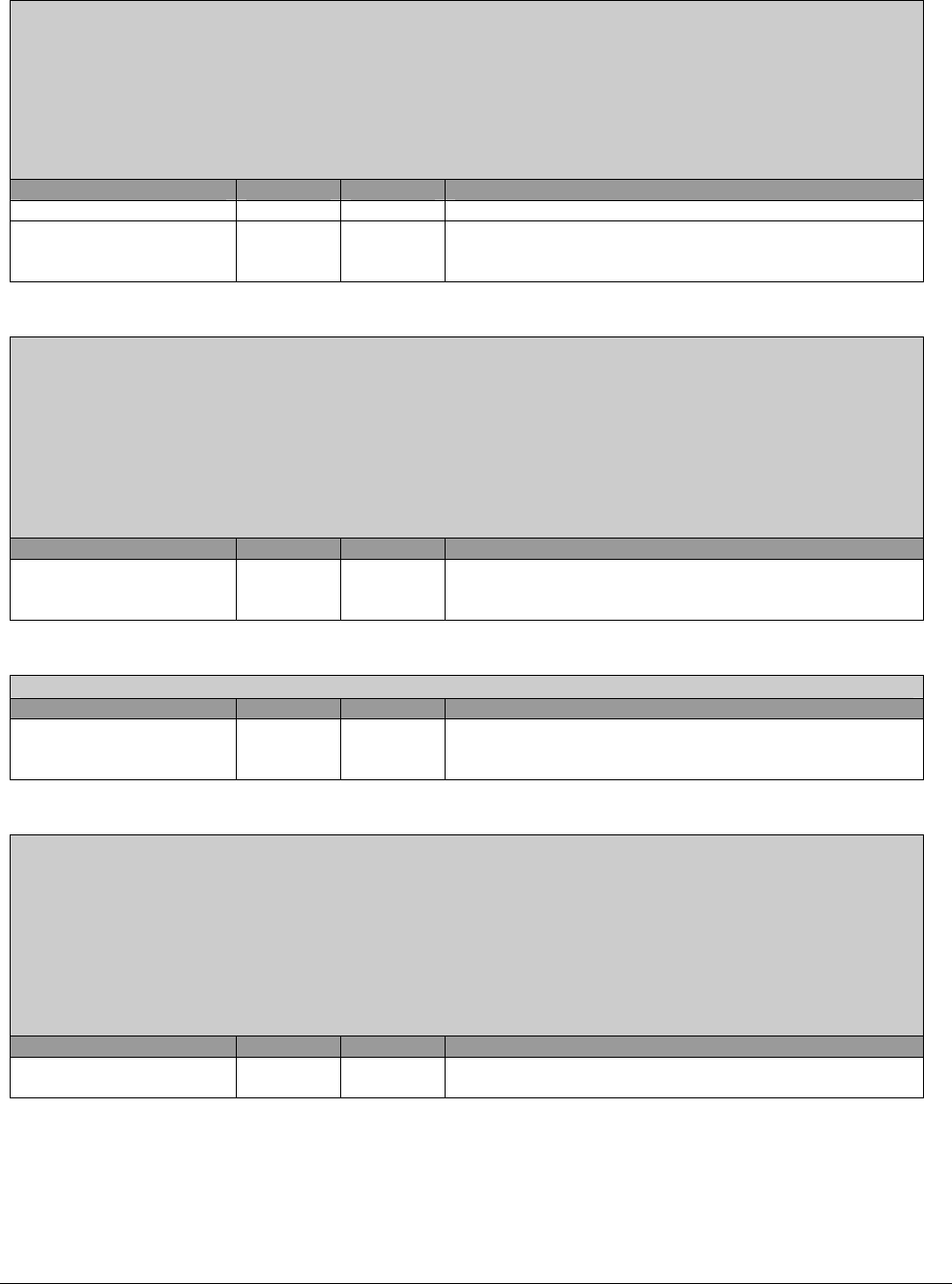

Stream Descriptor BDL Pointer Upper Base Address – RW – 32 bits

Input Stream 0 - [Mem_Reg: Base + 9Ch]

Input Stream 1 - [Mem_Reg: Base + BCh]

Input Stream 2 - [Mem_Reg: Base + DCh]

Input Stream 3 - [Mem_Reg: Base + FCh]

Output Stream 0 - [Mem_Reg: Base + 11Ch]

Output Stream 1 - [Mem_Reg: Base + 13Ch]

Output Stream 2 - [Mem_Reg: Base + 15Ch]

Output Stream 3 - [Mem_Reg: Base + 17Ch]

Field Name Bits Default Description

Buffer Descriptor List

Upper Base Address

31:0 00000000

h

Upper 32 bit address of the Buffer Descriptor List. This

value should not be modified except when the Run bit is

“0”.

Wall Clock Counter Alias – R – 32 bits – [Mem_Reg: Base + 2030h]

Field Name Bits Default Description

Wall Clock Counter Alias 31:0 00000000

h

An alias of the Wall Clock Counter register at offset 30h. It

behaves exactly the same as if the Wall Clock Counter

register were being read directly.

Stream Descriptor Link Position in Buffer Alias – R – 32 bits

Input Stream 0 - [Mem_Reg: Base + 2084h]

Input Stream 1 - [Mem_Reg: Base + 20A4h]

Input Stream 2 - [Mem_Reg: Base + 20C4h]

Input Stream 3 - [Mem_Reg: Base + 20E4h]

Output Stream 0 - [Mem_Reg: Base + 2104h]

Output Stream 1 - [Mem_Reg: Base + 2124h]

Output Stream 2 - [Mem_Reg: Base + 2144h]

Output Stream 3 - [Mem_Reg: Base + 2164h]

Field Name Bits Default Description

Link Position in Buffer

Alias

31:0 00000000

h

An alias of the Link Position in Buffer register of each

Stream Descriptor.