©2008 Advanced Micro Devices, Inc.

SMBus Module and ACPI Block (Device 20, Function 0)

AMD SB600 Register Reference Manual Proprietary Page 170

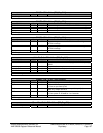

FakeAsrEn– RW – 8 bits – [PM_Reg:8Fh]

Field Name Bits Default Description

MaskNbBmStsSet 5 0b When set, BmStsSet message from NB will not cause wake up

from C state.

MemRstDisable 6 0b When set, the memory reset function at DDR_RST# pin will be

disabled and can be used as GPM5#

DisableOtherIrq8 7 0b When set, other source of interrupt 8 (serial IRQ, HPET) will

not be routed to the SCI. Only RTC interrupt will be routed to

the SCI

FakeAsrEn register

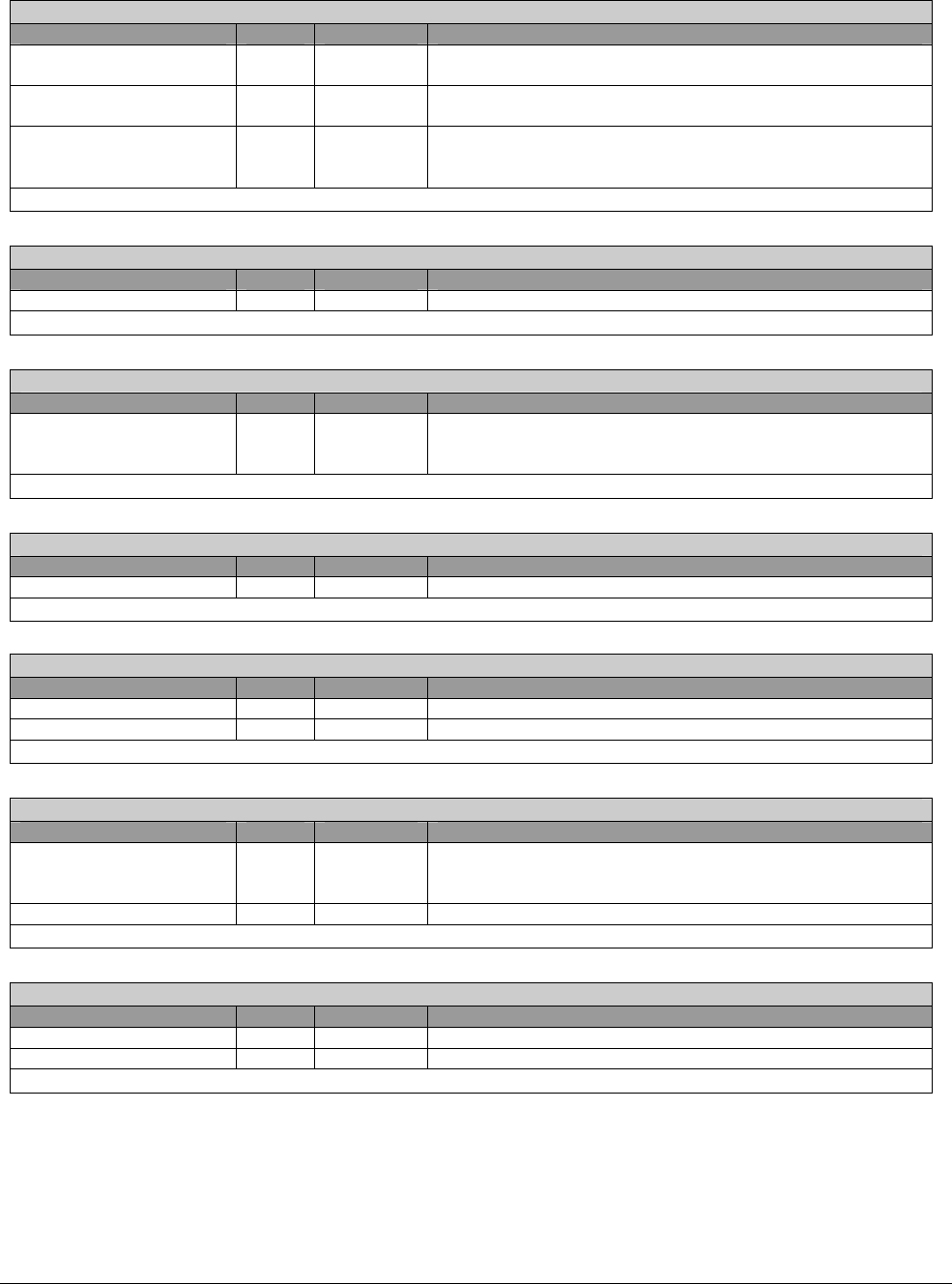

GEVENTOUT – RW – 8 bits – [PM_Reg:90h]

Field Name Bits Default Description

GEVENTOUT 7:0 00h GEVENT[7:0] output value

GEVENTOUT register

GEVENTEN – RW – 8 bits – [PM_Reg:91h]

Field Name Bits Default Description

GEVENTEN 7:0 FFh GEVENT[7:0] output enable

0: Enable

1: Tristate

GEVENTEN register

GEVENTIN – RW – 8 bits – [PM_Reg:92h]

Field Name Bits Default Description

GEVENTIN 7:0 -- GEVENT[7:0] input status

GEVENTIN register

GPM98OUT – RW – 8 bits – [PM_Reg:94h]

Field Name Bits Default Description

GPM98OUT 1:0 00b GPM[9:8] output value

Reserved 7:2

GPM98OUT register

GPM98EN – RW – 8 bits – [PM_Reg:95h]

Field Name Bits Default Description

GPM98EN 1:0 11b GPM[9:8] output enable

0: Enable

1: Tristate

Reserved 7:2 00h

GPM98EN register

GPM98IN – RW – 8 bits – [PM_Reg:96h]

Field Name Bits Default Description

GPM98IN 1:0 -- GPM[9:8] input status

Reserved 7:2 00h

GPM98IN register