©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 92

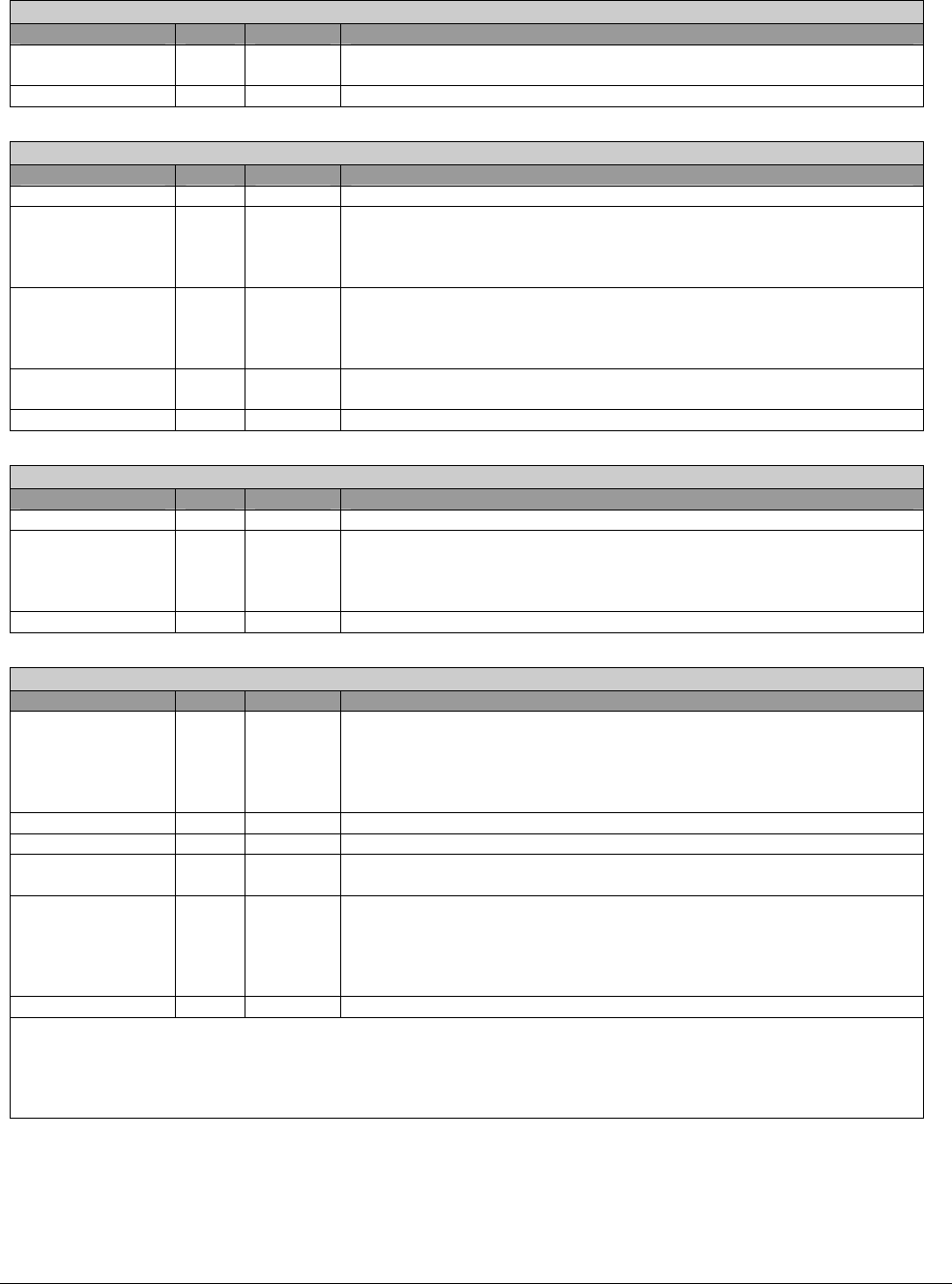

UTMI Control – RW - 32 bits - [EOR_Reg: EHCI_EOR + 94h]

Field Name Bits Default Description

VBusy 17 0b RO – To block software write to [16:8] when port router is updating the

field.

Reserved 31:18 Reserved

BIST Control / Loopback Test – RW - 32 bits - [EOR_Reg : EHCI_EOR + 98h]

Field Name Bits Default Description

Reserved 7:0 00h Reserved

Enable Loop Back

test

8 0b Enable external USB Port Loop back test.

The Loop Back test is to set one port to TX mode (Test Packet mode)

and one port in RX mode (Test SE0_NAK). Please reference to

PORTSCx[19:16] control the port into TX or RX mode.

Loopback Test

Status

9 0b Read Only.

Loop back status.

0: CRC Error on Loop Back Receiving Data

1: Good CRC on Loop Back Receiving data

Loopback Test

Done

10 0b Read Only.

Indicate Loop back test done.

Reserved 31:11 00000h

EOR MISC Control – RW - 32 bits - [EOR_Reg : EHCI_EOR + 9Ch]

Field Name Bits Default Description

Reserved 11:0 000h Reserved

EHCI Power

Saving Enable

12 0b Enable power saving clock gating. When enabled, dynamic clock gating

is enabled when EHCI is not at operational mode. The clock goes to all

memory module will be gated off, and the internal bus clock also gets

gated off unless the connection interrupt is detected.

Reserved 31:13 00000h Reserved

USB Common PHY Calibration – RW - 32 bits - [EOR_Reg: EHCI_EOR + A0h]

Field Name Bits Default Description

ComCalBus

6:0 xx Enables power saving clock gating (this was original at bit-31). When

enabled, dynamic clock gating is enabled when EHCI is not at

operational mode. The clock goes to all memory module will be gated

off, The blink clock also is gated off unless the connection interrupt is

detected.

Reserved 7 0b Reserved

NewCalBus 15:8 00h New calibration bus signed value. Bit-15 is the signed bit.

UsbCommonCalib

ration

16 0b If set, the PHY’s calibration value in bit[6:0] is returned to the PHY ports.

If clear, the value after adjustment is returned to the PHY ports.

AddToCommonCa

libration

17 0b If set, the signed NewCalBus is added to the ComCalBus and returned

to the PHY ports. Any overflow is clamped to all ones. Any underflow is

clamped to all zeros.

If clear, the NewCalBus (bit-14:8) replaces the ComCalBus and returns

to the PHY ports.

Reserved 31:18 0000h Reserved

Note:

1. The equation for calibration resistor is as follows: Rcal = 1/ [1/59.4 + CalValue/(1.05*3.8k ohm)], where the

CalValue is the final 7 bits of calibration setting send to PHY.

2. The total termination resistance value for HS USB D+/D- should include another 5 ohm resistance from FS

driver.

2.2.3.4 USB2.0 Debug Port Registers

This block of registers is memory-mapped. The base offset, Dbase, is directly defined in DBUG_PRT