©2008 Advanced Micro Devices, Inc.

Host PCI Bridge Registers (Device 20, Function 4)

AMD SB600 Register Reference Manual Proprietary Page 275

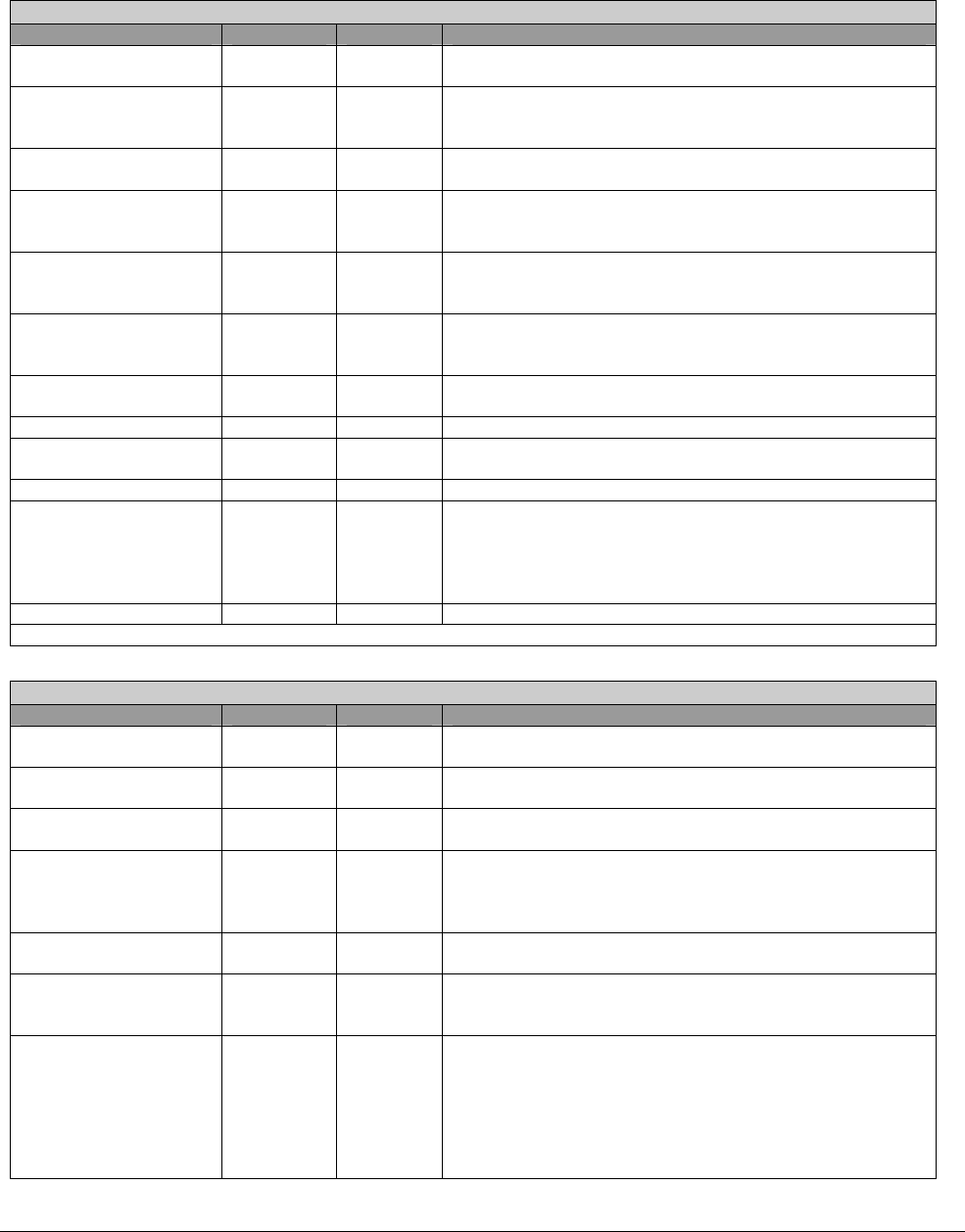

Prefetch Size Control - 32 bits - [PCI_Reg: 60h]

Field Name Bits Default Description

Read Size 2:0 2h If prefetch function is enabled, this defines the number of

initial prefetch cachelines for a PCI READ command

Read Size Adjustment 3 1b When set, PCIBridge will adjust the prefetch size for READ

automatically. If this bit is 0, then the prefetch size is always

defined by bits [2:0]

Read Line Size 6:4 4h If prefetch function is enabled, this defines the number of

initial prefetch cachelines for a PCI READLINE command

Read Line Adjustment 7 1b When set, PCIBridge will adjust the prefetch size for

READ_LINE automatically. If this bit is 0, then the prefetch

size is always defined by bits [6:4]

Read Multiple Size 10:8 6h If prefetch function is enabled, this defines the number of

initial prefetch cachelines for a PCI READ_MULTIPLE

command

Read Multiple

Adjustment

11 1b When set, PCIBridge will adjust the prefetch size for

READ_MULTIPLE automatically. If this bit is 0, then the

prefetch size is always defined by bits [10:8]

Prefetch Size Lower

Limit

14:12 0h The lower limit of the adjusted prefetch size.

Reserved 15 0b

Prefetch Size Upper

Limit

18:16 7h The upper limit of the adjusted prefetch size.

Reserved 19 0b

Prefetch Size Mlt

Enable

20 1b This also controls how PCIBridge adjusts the auto-prefetch

size. When set, PCIBridge will only adjust the prefetch size

if it knows it does not have enough or has too much data in

the prefetch buffer. Recommendation is to always set this

bit.

Reserved 31:21 0h

The fields in this register are effective only when prefetch is enabled (reg0x64[7]=1).

Misc Control Register - 32 bits - [PCI_Reg: 64h]

Field Name Bits Default Description

Downstream Config

Cycle Flush Enable

0 0h When this bit is 1, any downstream config cycle will flush all

the upstream read prefetch buffers.

Downstream Write

Cycle Flush Enable

1 1h When this bit is 1, any downstream non-config write cycle

will flush all the upstream read prefetch buffers.

Downstream Read

Cycle Flush Enable

2 0h When this bit is 1, any downstream non-config read cycle

will flush all the upstream read prefetch buffers.

Prefetch Buffer Timeout

Enable

3 1h When this bit is 1, upstream read prefetch buffer timeout

mechanism is enabled. If data stay in a buffer longer than

the time specified in Prefetch Timeout Limit (Reg5Ch), the

buffer will be flushed.

AB Masking Prefetch

Request Enable

4 1h The purpose of this is to improve the internal bus efficiency

and the recommendation is to have it set to 1

AB Masking Non-

prefetch Request

Enable

5 1h The purpose of this is to improve the internal bus efficiency

and the recommendation is to have it set to 1

Downstream Cycle

Flush Control

6 0h 0—If a downstream cycle is qualified to flush upstream

prefetch read buffer (depending on bit[2:0] in this register),

the flush happens when the cycle is sent out onto PCI bus

with at least one data phase..

1—If a downstream cycle is qualified to flush upstream

prefetch read buffer (depending on bit[2:0] in this register),

the flush happens as soon as the cycle arrives at PCI bus.