©2008 Advanced Micro Devices, Inc.

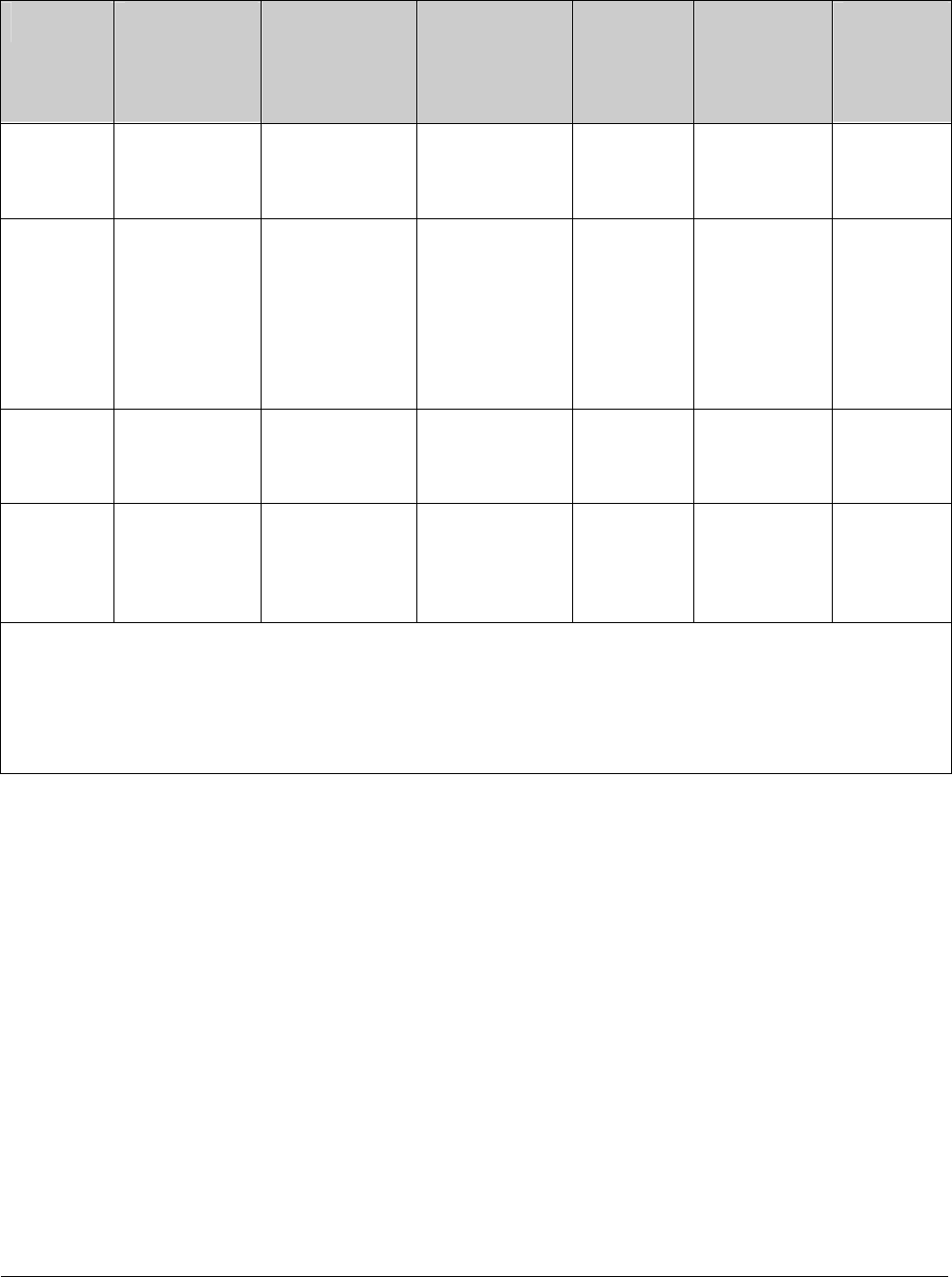

GEVENT/GPE/GPM/ExtEvent

AMD SB600 Register Reference Manual Proprietary Page 286

Pin Name

(*Note 1)

Multi-Function

Selection

Configure Bit

00 – SCI or SMI#

01 – SMI#

10 – SMI#

followed by SCI

11 - IRQ13

Trigger Configure

0–Falling edge

1–Rising edge

Enable

ACPI Event

Status

(Write 1 to ACPI

GPE00h Bit to

Clear)

Power

Domain

EXTEVENT

1#/

LPC_SMI#

SMBus

Reg64h[Bit 22]

=1 to enable

GPE

PM IO

Reg32h[Bit3:2]

PM IO

Reg37h[Bit 1]

ACPI

GPE04h[Bit17]

PM IO

Reg3Ah[Bit 1]

or ACPI

GPE00h[Bit17]

S0

GPIO0

PM IO

Reg60h[Bit 7]=1

for GPIO; in

addition, PM IO

Reg84h[Bit 1]=0

and SMBus

Reg64h[Bit

19]=1 to enable

GPE

PM IO

Reg34h[Bit1:0]

PM IO

Reg38h[Bit 0]

ACPI

GPE04h[Bit24]

PM IO

Reg3Bh[Bit 0]

or ACPI

GPE00h[Bit24]

S0

GPIO2

PM IO

Reg60h[Bit 5]=0

for GPIO

PM IO

Reg35h[Bit5:4]

PM IO

Reg38h[Bit 6]

ACPI

GPE04h[Bit

30]

PM IO

Reg3Bh[Bit 6]

or ACPI

GPE00h[Bit 30]

S0

GPIO64/

TALERT#/

TEMPIN3

PM2 IO

Reg42h[Bit 7:6]

00: GPIO

01/10/11:

TEMPIN3

PM IO

Reg3Ch[Bit3:2]

SMI# followed by

SCI not available

PM IO

Reg67h[Bit 5]

ACPI

GPE04h[Bit 9]

ACPI

GPE00h[Bit 9]

S0

Notes:

1– In this table, the “GEVENT,” ”GPM,” “EXTEVNT,” or “GPIO” portion of the pin name has been put at the front of the names for the

sake of clarity, making the pin names different from how they appear in the AMD SB600 Databook.

2–PM IO Register can be accessed through IO port CD6h/CD7h.

3–GPE Register is in the ACPI IO space. The base address of GPE IO space is defined in PM IO Reg28h/29h.

4–In K8 system, this pin is always used as S3_STATE output (indicating ACPI S3 state).

5–This pin is GEVENT pin only and not a multiplexed pin. The alternative function is mentioned only as a suggestion.

4.2.3 GPM as GPIO

GPM pins can be used as GPIO. The GPM I/O function is controlled by three registers: I/O C50h, C51h,

C52h, PM I/O 94h, 95h, 96h.

4.2.3.1 GPM Pins as Input

For GPM[7:0], follow this sequence -

1. Set index register 0C50h to 13h (Miscellaneous Control).

2. Set CM Data register 0C51h Bits [7:6] to 01b to set Input/Out control.

3. Set GPM port 0C52h appropriate bits to 1 to tri-state the GPM port.

4. Set CM Data register 0C51h Bits [7:6] = 00b to set GPM port for read.

5. Read the input status through port 0C52h.

For GPM[9:8], simply read the input status from PM I/O 96h Bits [1:0].