©2008 Advanced Micro Devices, Inc.

OCHI USB 1.1 and EHCI USB 2.0 Controllers

AMD SB600 Register Reference Manual Proprietary Page 79

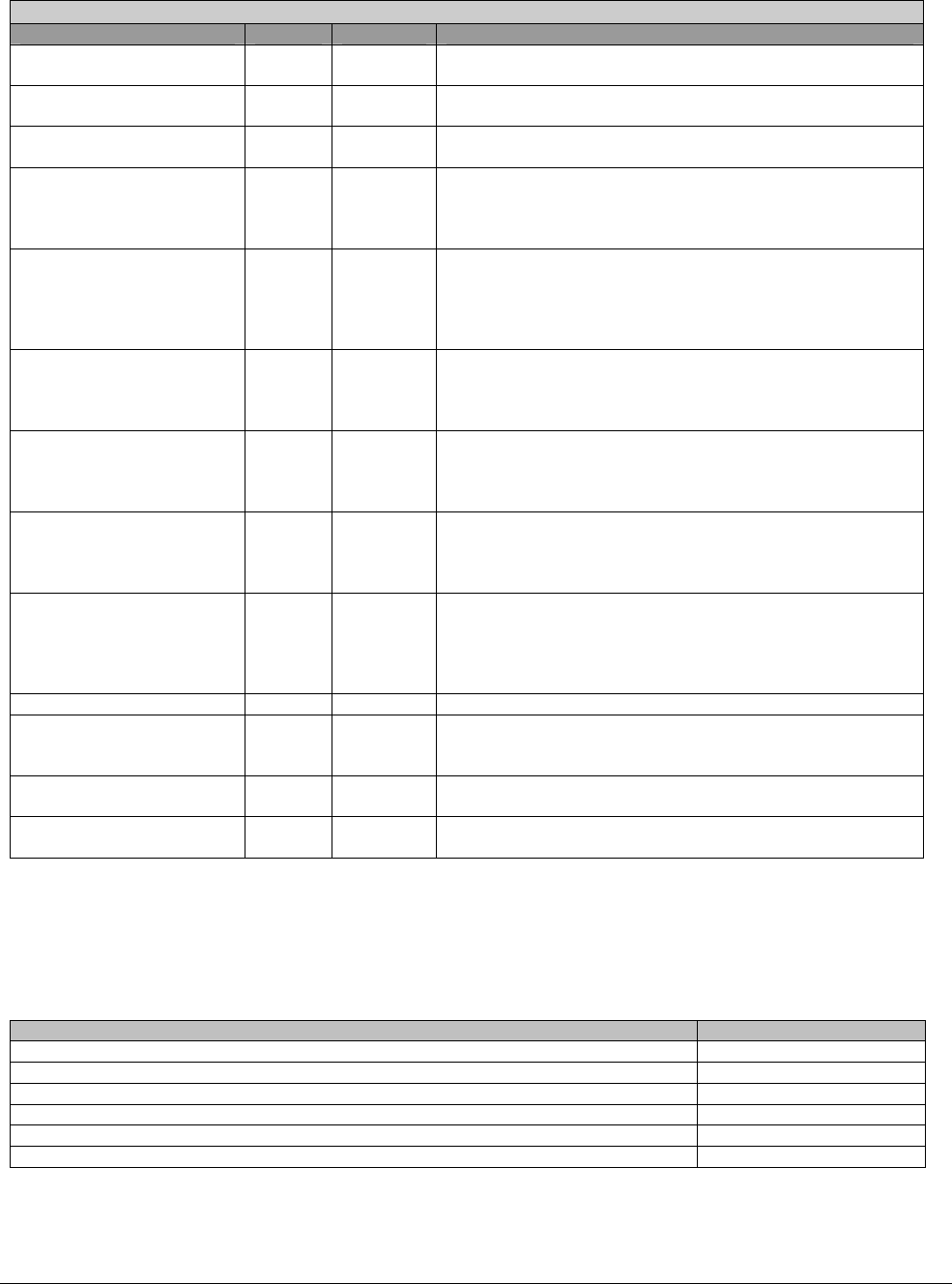

USBLEGCTLSTS – RW - 32 bits - [PCI_Reg : EECP + 04h]

Field Name Bits Default Description

SMI on OS Ownership

Enable

13 0b When this bit is a one AND the OS Ownership Change bit is

one, the host controller will issue an SMI.

SMI on PCI Command

Enable

14 0b When this bit is one and SMI on PCI Command is one, then

the host controller will issue an SMI.

SMI on BAR Enable 15 0b When this bit is one and SMI on BAR is one, then the host

controller will issue an SMI.

SMI on USB Complete 16 0b Shadow bit of USB Interrupt (USBINT) bit in the USBSTS

register. To set this bit to a zero, system software must

write a one to the USB Interrupt bit in the USBSTS register.

Read Only.

SMI on USB Error 17 0b Shadow bit of USB Error Interrupt (USBERRINT) bit in the

USBSTS register. To set this bit to a zero, system software

must write a one to the USB Error Interrupt bit in the

USBSTS register.

Read Only.

SMI on Port Change

Detect.

18 0b Shadow bit of Port Change Detect bit in the USBSTS

register. To set this bit to a zero, system software must write

a one to the Port Change Detect bit in the USBSTS register.

Read Only.

SMI on Frame List Rollover 19 0b Shadow bit of Frame List Rollover bit in the USBSTS

register. To set this bit to a zero, system software must write

a one to the Frame List Rollover bit in the USBSTS register.

Read Only.

SMI on Host System Error 20 0b Shadow bit of Host System Error bit in the USBSTS register.

To set this bit to a zero, system software must write a one to

the Host System Error bit in the USBSTS register.

Read Only.

SMI on Async Advance 21 0b Shadow bit of the Interrupt on Async Advance bit in the

USBSTS register. To set this bit to a zero, system software

must write a one to the Interrupt on Async

Advance bit in the USBSTS register.

Read Only.

Reserved. 28:22 These bits are reserved and must be set to zero.

SMI on OS Ownership

Change

29 0b This bit is set to one whenever the HC OS Owned

Semaphore bit in the USBLEGSUP register transitions from

1 to 0 or 0 to 1.

SMI on PCI Command 30 0b This bit is set to one whenever the PCI Command Register

is written.

SMI on BAR R/WC 31 0b This bit is set to one whenever the Base Address Register

(BAR) is written.

2.2.3.2 Host Controller Capability Registers (MEM_Reg)

This block of registers is memory-mapped. Access address is equal to offset address plus base address defined in

BAR[PCI_Reg : 10h].

Registers Name Offset Address

Capability Register Length - CAPLENGTH 00h

Reserved 01h

Host Controller Interface Version – HCIVERSION 02h

Structural Parameters – HCSPARAMS 04h

Capability Parameters - HCCPARMAS 08h

Companion Port Route Description – HCSP-PORTROUTE 0Ch