Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

100 Order Number: 252480-006US

3.6.8.2 Overflow Flag (OV)

The Overflow flag is a sticky flag that is set when the debugger writes to the RX register

while the RR bit is set.

The flag is used during high-speed download to indicate that some data was lost. The

assumption during high-speed download is that the time it takes for the debugger to

shift in the next data word is greater than the time necessary for the debug handler to

process the previous data word. So, before the debugger shifts in the next data word,

the handler will be polling for that data.

However, if the handler incurs stalls that are long enough such that the handler is still

processing the previous data when the debugger completes shifting in the next data

word, an overflow condition occurs and the OV bit is set.

Once set, the overflow flag will remain set, until cleared by a write to TXRXCTRL with

an MCR. After the debugger completes the download, it can examine the OV bit to

determine if an overflow occurred. The debug handler software is responsible for saving

the address of the last valid store before the overflow occurred.

3.6.8.3 Download Flag (D)

The value of the download flag is set by the debugger through JTAG. This flag is used

during high-speed download to replace a loop counter.

The download flag becomes especially useful when an overflow occurs. If a loop

counter is used, and an overflow occurs, the debug handler cannot determine how

many data words overflowed. Therefore the debug handler counter may get out of sync

with the debugger — the debugger may finish downloading the data, but the debug

handler counter may indicate there is more data to be downloaded - this may result in

unpredictable behavior of the debug handler.

Using the download flag, the debug handler loops until the debugger clears the flag.

Therefore, when doing a high-speed download, for each data word downloaded, the

debugger should set the D bit.

3.6.8.4 TX Register Ready Bit (TR)

The debugger and debug handler use the TR bit to synchronize accesses to the TX

register. The debugger and debug handler must poll the TR bit before accessing the TX

register. Table 41 shows the handshaking used to access the TX register.

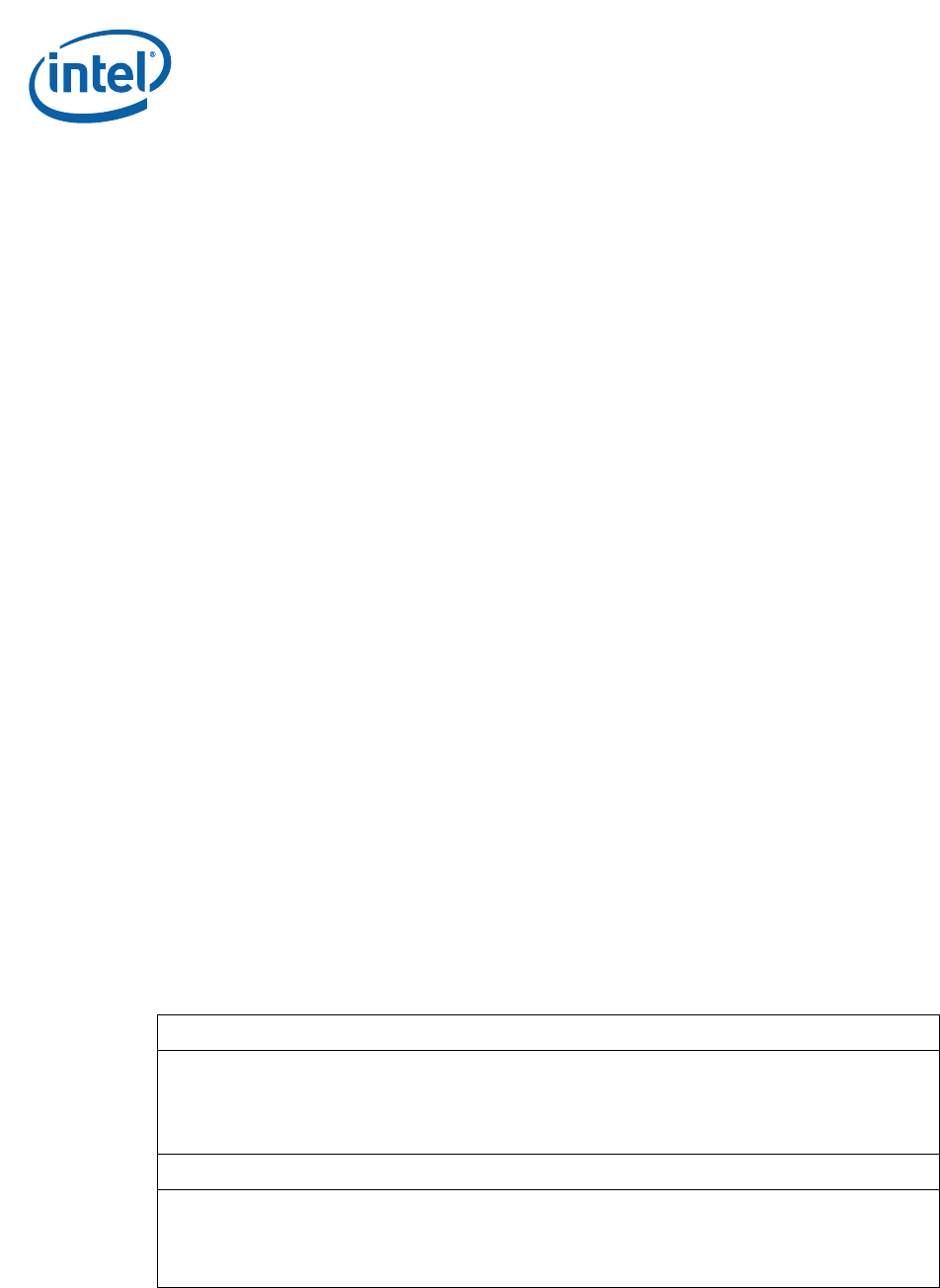

Table 41. TX Handshaking

Debugger Actions

• Debugger is expecting data from the debug handler.

• Before reading data from the TX register, the debugger polls the TR bit through JTAG until the bit is set.

NOTE: while polling TR, the debugger must scan out the TR bit and the TX register data.

• Reading a ‘1’ from the TR bit, indicates that the TX data scanned out is valid

• The action of scanning out data when the TR bit is set, automatically clears TR.

Debug Handler Actions

• Debug handler wants to send data to the debugger (in response to a previous request).

• The debug handler polls the TR bit to determine when the TX register is empty (any previous data has

been read out by the debugger). The handler polls the TR bit until it is clear.

• Once the TR bit is clear, the debug handler writes new data to the TX register. The write operation

automatically sets the TR bit.