Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 105

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

A debugger sets an external debug break by scanning data into the DBG_SR with

DBG_SR[2] set and the desired value to set the DCSR JTAG writable bits in

DBG_SR[34:3].

Once an external debug break is set, it remains set internally until a debug exception

occurs. In Monitor mode, external debug breaks detected during abort mode are

pended until the processor exits abort mode. In Halt mode, breaks detected during

SDS are pended until the processor exits SDS. When an external debug break is

detected outside of these two cases, the processor ceases executing instructions as

quickly as possible. This minimizes breakpoint skid, by reducing the number of

instructions that can execute after the external debug break is requested. However, the

processor will continue to process any instructions which may have already begun

execution. Debug mode will not be entered until all processor activity has ceased in an

orderly fashion.

3.6.11.2.3 DBG.DCSR

The DCSR is updated with the value loaded into DBG.DCSR following an Update_DR.

Only bits specified as writable by JTAG in Table 33 are updated.

3.6.11.3 DBGTX JTAG Command

The ‘DBGTX’ JTAG instruction selects the DBGTX JTAG data register. The JTAG op code

for this instruction is ‘0b10000’. Once the DBGTX data register is selected, the

debugger can receive data from the debug handler.

3.6.11.4 DBGTX JTAG Register

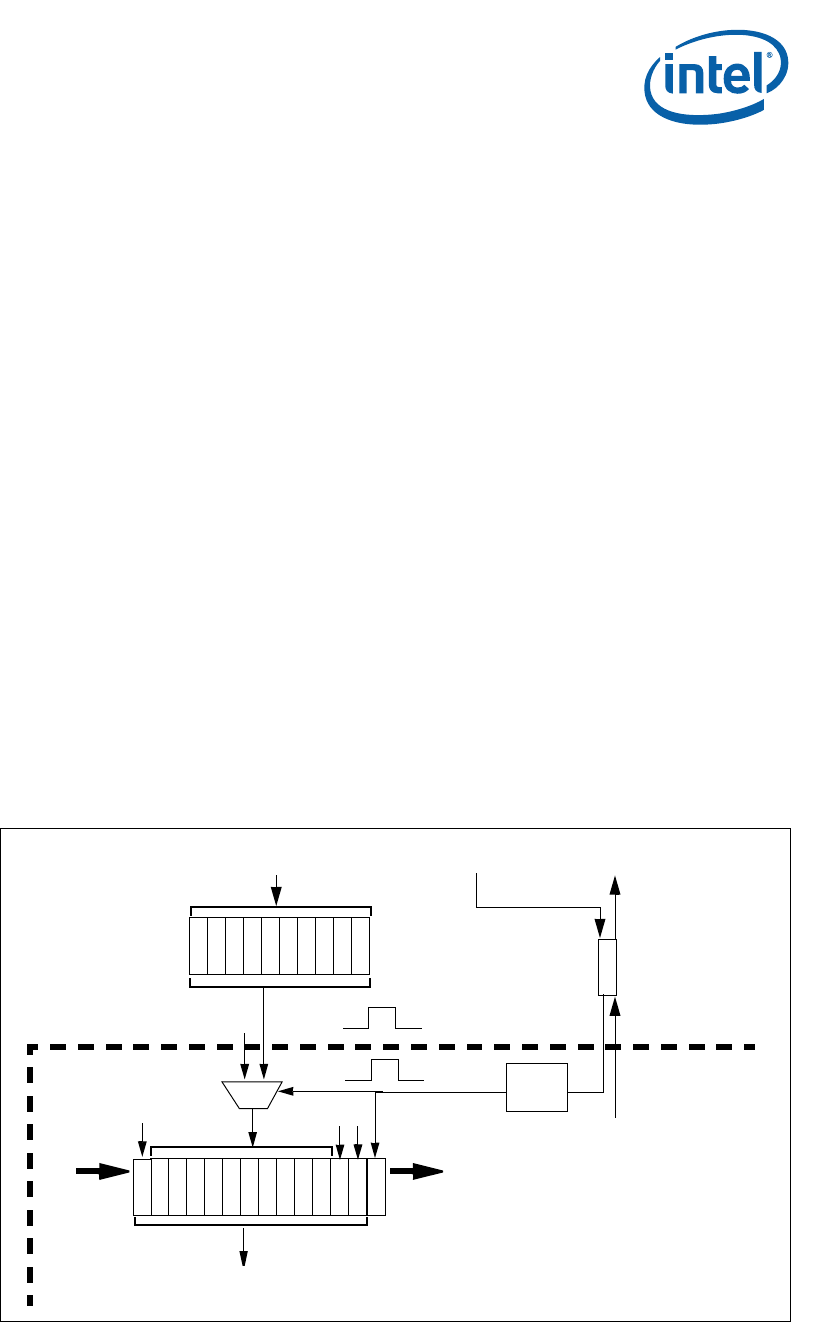

The DBGTX JTAG instruction selects the Debug JTAG Data register (Figure 17). The

debugger uses the DBGTX data register to poll for breaks (internal and external) to

debug mode and once in debug mode, to read data from the debug handler.

Figure 17. DBGTX Hardware

TDOTDI

DBG_SR

Capture_DR

Update_DR

123

3435

031

TXRXCTRL

TX

Core CLK

software read-only

0

0

0

1

28

set by SW write to TX

clear by Debugger read

Ignored

software write

TCLK

delay

0x0000 0000

10