Intel

®

IXP42X product line and IXC1100 control plane processors—Internal Bus

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

206 Order Number: 252480-006US

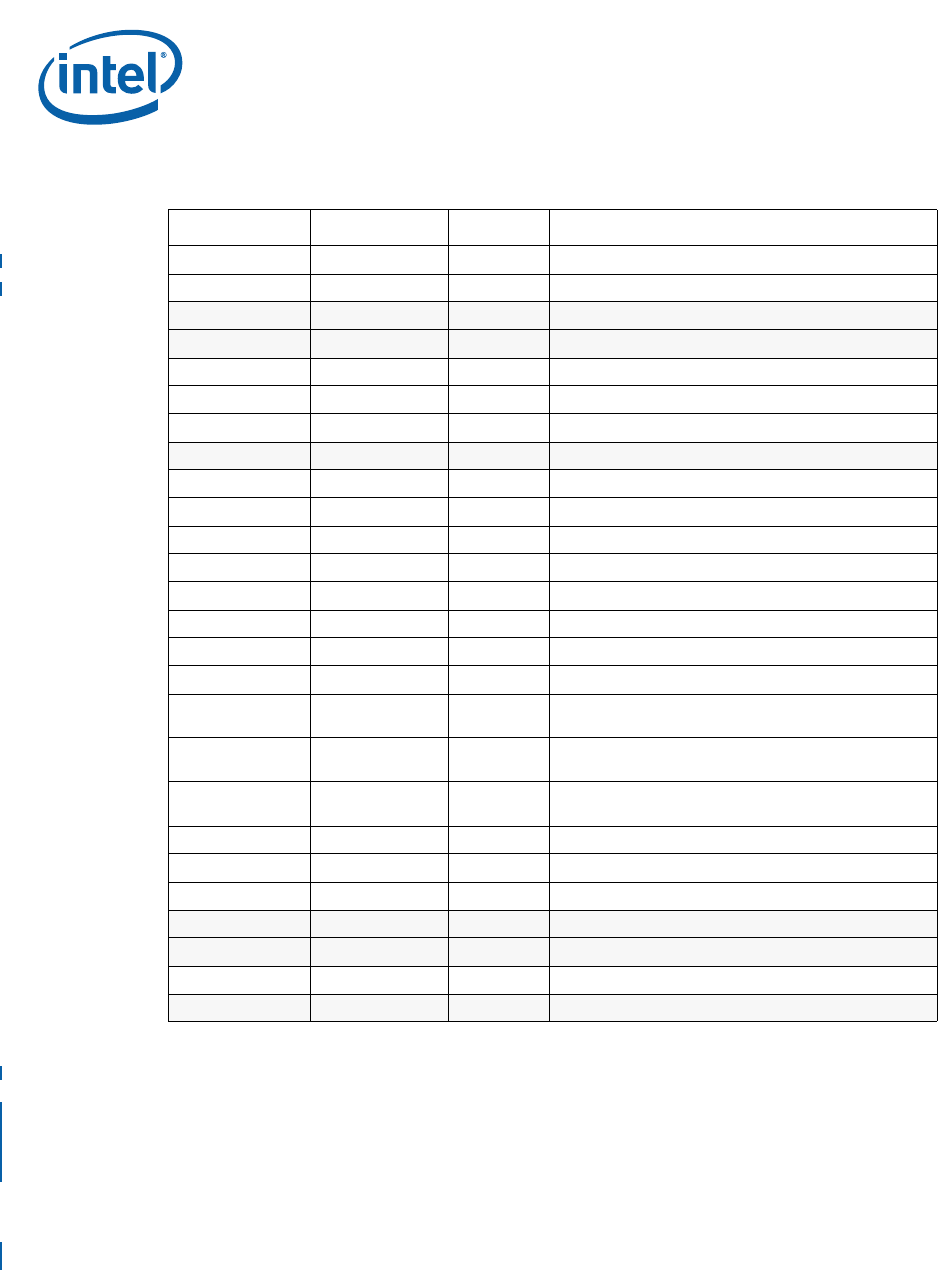

Table 96. Memory Map

Start Address End Address Size Use

0000_0000 0FFF_FFFF 256 MB Expansion Bus Data (Mirrored)/SDRAM Data

†

1000_0000 2FFF_FFFF 768 MB SDRAM Data (Aliased)

†

3000_0000 3FFF_FFFF 256 MB (Reserved)

4000_0000 47FF_FFFF 128 MB (Reserved)

4800_0000 4FFF_FFFF 128 MB PCI Data

5000_0000 5FFF_FFFF 256 MB Expansion Bus Data

6000_0000 63FF_FFFF 64 MB Queue manager

6400_0000 BFFF_FFFF (Reserved)

C000_0000 C3FF_FFFF 64 MB PCI Controller Configuration and Status Registers

C400_0000 C7FF_FFFF 64 MB Expansion Bus Configuration Registers

C800_0000 C800_0FFF 1 KB High-Speed UART

C800_1000 C800_1FFF 1 KB Console UART

C800_2000 C800_2FFF 1 KB Internal Bus Performance Monitoring Unit

C800_3000 C800_3FFF 1 KB Interrupt Controller

C800_4000 C800_4FFF 1 KB GPIO Controller

C800_5000 C800_5FFF 1 KB Timers

C800_6000 C800_6FFF 1 KB

WAN/Voice NPE = NPE-A (IXP400 software

Definition)– Not User Programmable

C800_7000 C800_7FFF 1 KB

Ethernet NPE A = NPE-B (IXP400 software

Definition) – Not User Programmable

C800_8000 C800_8FFF 1 KB

Ethernet NPE B = NPE-C (IXP400 software

Definition) – Not User Programmable

C800_9000 C800_9FFF 1 KB Ethernet MAC A

C800_A000 C800_AFFF 1 KB Ethernet MAC B

C800_B000 C800_BFFF 1 KB USB Controller

C800_C000 C800_FFFF (Reserved)

C801_0000 CBFF_FFFF (Reserved)

CC00_0000 CC00_00FF 256 Byte SDRAM Configuration Registers

CC00_0100 FFFF_FFFF (Reserved)

† The lowest 256 MB of address space is configurable based on the value of a configuration register

located in the Expansion Bus Controller.

• When bit 31 (MEM_MAP) of configuration register #0 (EXP_CNFG0) is set to logic 1, the Expansion Bus

occupies the lowest 256 MB of address space.

• When bit 31 (MEM_MAP) of configuration register #0 (EXP_CNFG0) is set to logic 0 the Expansion Bus

occupies 256 MB of address space starting at 5000_0000 while the SDRAM occupies the lowest 256 MB

of address address space

In both cases, regardless of the value of MEM_MAP, the SDRAM occupies the 768 MB (1000_0000 to

2FFF_FFFF) immediately following the lowest 256 MB and the Expansion Bus can be accessed starting

at address 5000_0000.

The largest SDRAM memory size supported by the Intel

®

IXP42X product line and IXC1100 control

plane processors is 256 MB. The actual memory implemented in any given configuration will be aliased

(repeated) to fill the 1 GB SDRAM address space. Due to aliasing, all of the SDRAM will be accessible

even when the Expansion Bus occupies the lowest 256 MB of address space. On reset, bit 31

(MEM_MAP) of configuration register #0 (EXP_CNFG0) in the Expansion Bus will be set to logic 1. This

setting is required because the dedicated boot memory is flash memory located on the Expansion Bus.

§ §