Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

134 Order Number: 252480-006US

3.7.2 Register Description

3.7.2.1 Clock Counter (CCNT)

The format of CCNT is shown in Table 54. The clock counter is reset to ‘0’ by setting bit

2 in the Performance Monitor Control Register (PMNC) or can be set to a predetermined

value by directly writing to it. It counts core clock cycles. When CCNT reaches its

maximum value 0xFFFF,FFFF, the next clock cycle will cause it to roll over to zero and

set the overflow flag (bit 0) in FLAG. An interrupt request will occur if it is enabled via

bit 0 in INTEN.

3.7.2.2 Performance Count Registers

(PMN0 - PMN3)

There are four 32-bit event counters; their format is shown in Table 55. The event

counters are reset to ‘0’ by setting bit 1 in the PMNC register or can be set to a

predetermined value by directly writing to them. When an event counter reaches its

maximum value 0xFFFF,FFFF, the next event it needs to count will cause it to roll over

to zero and set its corresponding overflow flag (bit 1,2,3 or 4) in FLAG. An interrupt

request will be generated if its corresponding interrupt enable (bit 1,2,3 or 4) is set in

INTEN.

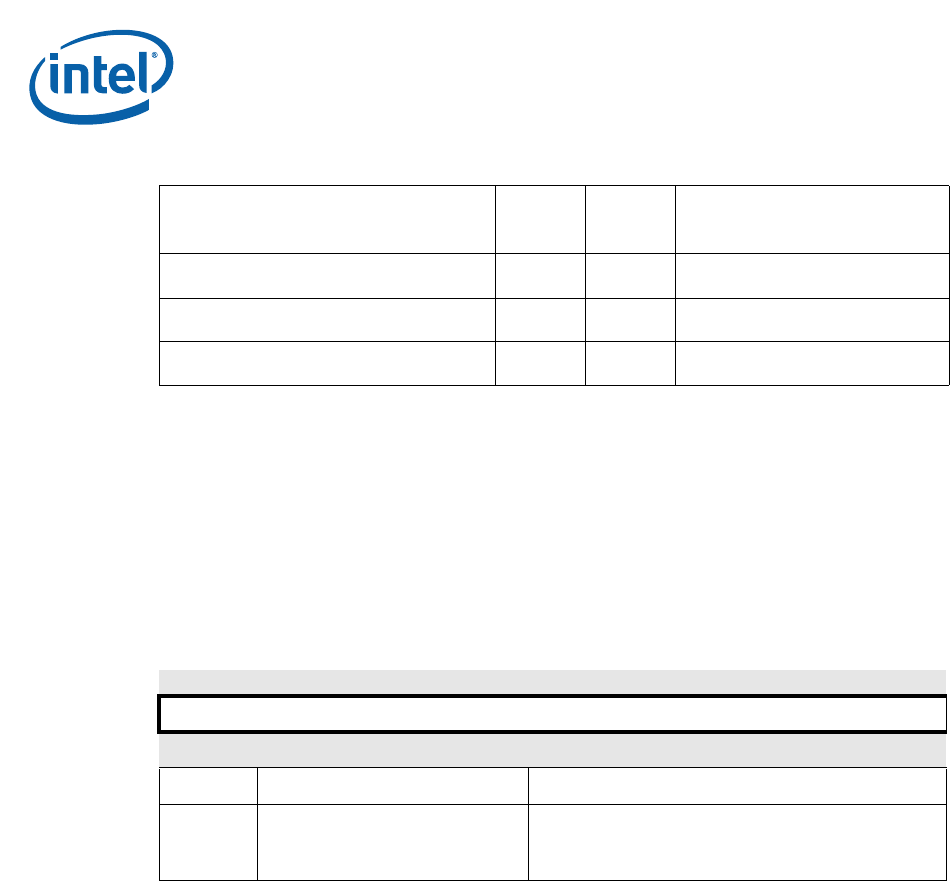

(PMN1) Performance Count Register 1 0b0001 0b0010

Read: MRC p14, 0, Rd, c1, c2, 0

Write: MCR p14, 0, Rd, c1, c2, 0

(PMN2) Performance Count Register 2 0b0010 0b0010

Read: MRC p14, 0, Rd, c2, c2, 0

Write: MCR p14, 0, Rd, c2, c2, 0

(PMN3) Performance Count Register 3 0b0011 0b0010

Read: MRC p14, 0, Rd, c3, c2, 0

Write: MCR p14, 0, Rd, c3, c2, 0

Table 53. Performance Monitoring Registers (Sheet 2 of 2)

Description

CRn

Register

#

CRm

Register

#

Instruction

Table 54. Clock Count Register (CCNT)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Clock Counter

reset value: unpredictable

Bits Access Description

31:0 Read / Write

32-bit clock counter - Reset to ‘0’ by PMNC register.

When the clock counter reaches its maximum value

0xFFFF,FFFF, the next cycle will cause it to roll over to

zero and generate an interrupt request if enabled.