Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

156 Order Number: 252480-006US

3.8.3.4.4 Data Aborts

Two types of data aborts exist in the Intel XScale processor: precise and imprecise. A

precise data abort is defined as one where R14_ABORT always contains the PC (+8) of

the instruction that caused the exception. An imprecise abort is one where R14_ABORT

contains the PC (+4) of the next instruction to execute and not the address of the

instruction that caused the abort. In other words, instruction execution will have

advanced beyond the instruction that caused the data abort.

On the Intel XScale processor precise data aborts are recoverable and imprecise data

aborts are not recoverable.

Precise Data Aborts

• A lock abort is a precise data abort; the extended Status field of the Fault Status

Register is set to 0xb10100. This abort occurs when a lock operation directed to the

MMU (instruction or data) or instruction cache causes an exception, due to either a

translation fault, access permission fault or external bus fault.

The Fault Address Register is undefined and R14_ABORT is the address of the

aborted instruction + 8.

• A data MMU abort is precise. These are due to an alignment fault, translation fault,

domain fault, permission fault or external data abort on an MMU translation. The

status field is set to a predetermined ARM definition which is shown in Table 75.

The Fault Address Register is set to the effective data address of the instruction and

R14_ABORT is the address of the aborted instruction + 8.

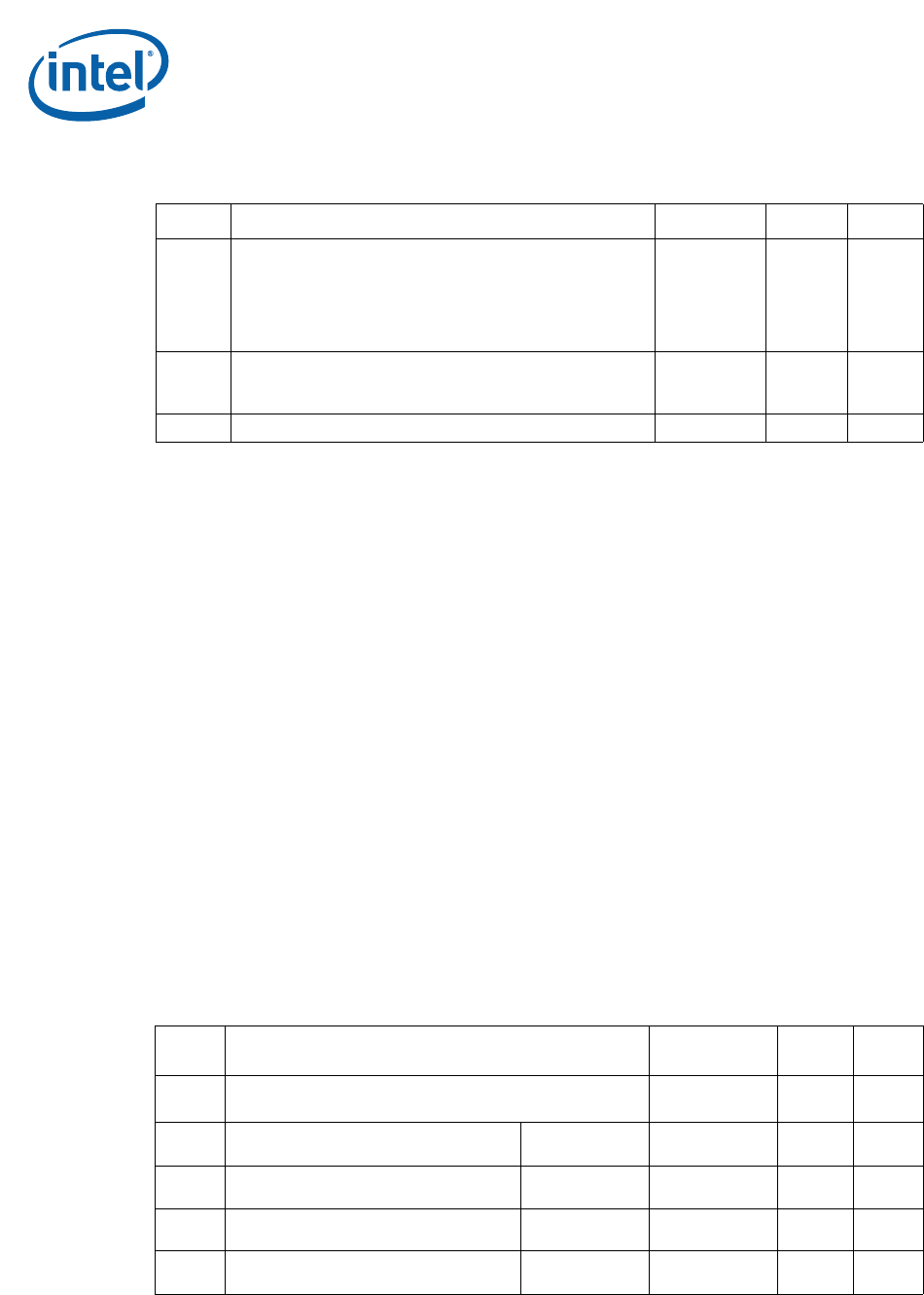

Table 74. Processors’ Encoding of Fault Status for Prefetch Aborts

Priority Sources FS[10,3:0]

*

Domain FAR

Highest

Instruction MMU Exception

Several exceptions can generate this encoding:

- translation faults

- domain faults, and

- permission faults

It is up to software to figure out which one occurred.

0b10000 invalid invalid

External Instruction Error Exception

This exception occurs when the external memory system

reports an error on an instruction cache fetch.

0b10110 invalid invalid

Lowest Instruction Cache Parity Error Exception 0b11000 invalid invalid

Note: All other encodings not listed in the table are reserved.

Table 75. Intel XScale

®

Processor Encoding of Fault Status for Data Aborts (Sheet 1 of 2)

Priorit

y

Sources FS[10,3:0]

*

Domain FAR

Highest Alignment

0b000x1

invalid valid

External Abort on Translation

First level

Second level

0b01100

0b01110

invalid

valid

valid

valid

Translation

Section

Page

0b00101

0b00111

invalid

valid

valid

valid

Domain

Section

Page

0b01001

0b01011

valid

valid

valid

valid

Permission

Section

Page

0b01101

0b01111

valid

valid

valid

valid

Note: All other encodings not listed in the table are reserved.