Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 527

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.28 UDC Byte Count Register 12 (UBCR12)

The byte count register maintains the remaining byte count in the active buffer of out

endpoint 12.

18.5.28.1 Endpoint 12 Byte Count (BC[7:0])

The byte count is updated after each byte is read. When software receives an interrupt

that indicates the endpoint has data, it can read the byte count register to determine

the number of bytes that remain to be read.

The number of bytes that remain in the input buffer is equal to the byte count +1.

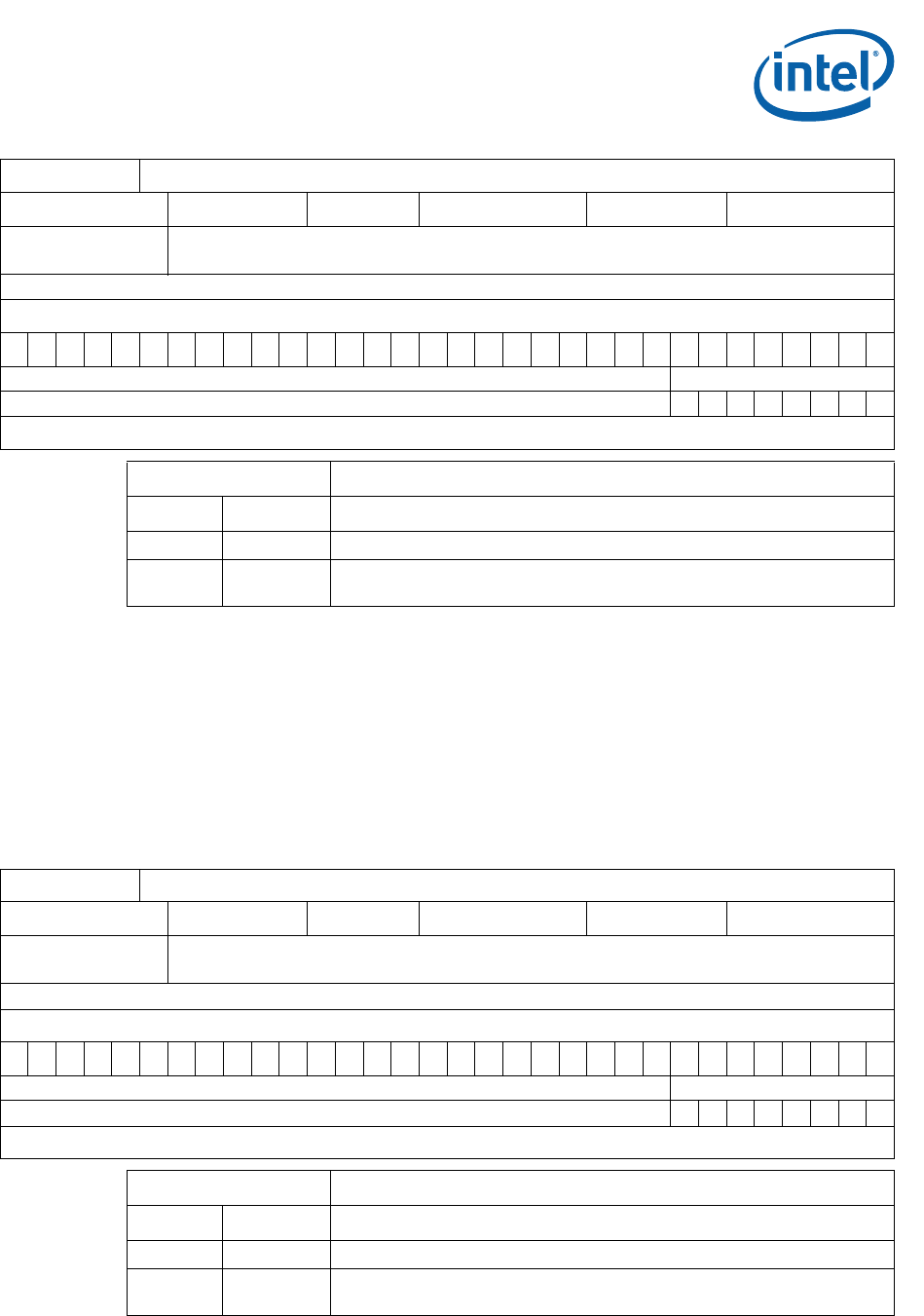

Register Name: UBCR9

Hex Offset Address: 0 x C800B074 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Endpoint 9 Byte Count

Access: Read-Only

Bits

31 87 0

(Reserved) BC[7:0]

X 00000000

Resets (Above)

Register

UBCR9

Bits Name Description

31:0 (Reserved)

7:0 BC

Byte Count (read-only).

Number of bytes in the FIFO is Byte Count plus 1 (BC+1).

Register Name: UBCR12

Hex Offset Address: 0 x C800B078 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Endpoint 12 Byte Count

Access: Read-Only

Bits

31 87 0

(Reserved) BC[7:0]

X 00000000

Resets (Above)

Register

UBCR12

Bits Name Description

31:8 (Reserved)

7:0 BC

Byte Count (read-only).

Number of bytes in the FIFO is Byte Count plus 1 (BC+1).