Intel

®

IXP42X product line and IXC1100 control plane processors—UTOPIA Level-2

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

544 Order Number: 252480-006US

control plane processors by driving their UTP_IP_FCI (also known as RX_EMPTY_N/

RX_CLAV) signal, to inform the UTOPIA Level-2 Interface that the physical interface is

ready to send a cell.

The Receive Port Status (RXPORTSTAT) register, contained within the Receive Module,

stores the polling result for each of the physical interfaces. The UTOPIA Level-2

hardware uses the values — stored in the Receive Port Status (RXPORTSTAT) Register

— to determine the physical interface the received cell originated from. The Receive

Module will store the received cell along with the physical interface address that the cell

was received from into the Receive FIFO with some basic filtering capability if desired.

The Network Processor Engine will then read the address from which the cell originated

and then the cell.

The Receive Module performs an optional, cell-level filtering that may cause a cell to be

discarded prior to being placed into the Receive FIFO. Some of these features can be

enabled or disabled include:

• Received cells that are too short are discarded

• Excess bytes of received cells that are too long are discard

• Detection of HEC errors in the cell header causes the cell to be discarded (Can be

enabled/disabled)

• Detection of idle cells will be discarded (Can be enabled/disabled. The definition of

an idle cell is programmable by setting the appropriate values in the Receive Define

Idle [RxDefineIdle] registers)

As the Receive Module is placing data into the Receive FIFO, the header information is

being passed to the Receive Pre-Hash Unit.

The UTOPIA Coprocessor Receive Pre-Hash Module provides a mechanism for allowing

incoming UTOPIA cells to have the ATM header looked up in a hash table to achieve

faster address recognition. The hash unit takes the incoming ATM header, combines it

with the arriving port information, and produces a header that can be read by the

Network Processor Engine core. The Receive Pre-Hash Function can be enabled or

disabled and can be used in single-PHY or multiple-PHY modes of operation. When used

in single-PHY mode of operation, the port address will always be zero.

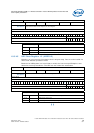

Figure 99 shows the reception of a cell in multiple-PHY (MPHY) mode. The following

assumptions are made for the figure:

• There are eight active physical interfaces connected named A through H which map

to logical address 0 through 7.

• Physical Interface A is the currently selected physical interface for clock cycles 0

through18.

• Notice on clock 7 that the result from Physical Interface G is that Physical Interface

G has a full cell ready for the IXP42X product line and IXC1100 control plane

processors. The UTP_RX_FCI signal flags that a full cell is ready to be sent by

Physical Interface G to the IXP42X product line and IXC1100 control plane

processors, asserting the UTP_RX_FCI to logic 1 one clock after Physical Interface

G has been polled.

• On clock 16, the final Physical Interface polled is the Physical Interface that is

currently selected. This polling is irrelevant to the Physical Interface that was polled

previously prior to this location.

• Notice on clock cycles 18 and 19 that Physical Interface G is selected as the next

Physical Interface that the IXP42X product line and IXC1100 control plane

processors will receive data from that Physical Interface.