Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

214 Order Number: 252480-006US

Once the PCI controller has determined that the mode of operation is to be host, the

IXP42X product line and IXC1100 control plane processors are required to configure the

rest of the PCI bus. However, before the IXP42X product line and IXC1100 control plane

processors can configure the rest of the PCI bus, the PCI Controller must be configured.

The Configuration and Status Registers must be initialized and the PCI Controller

Configuration and Status Registers must be initialized. (For more detail on initializing

the Configuration and Status Registers, see “Initializing PCI Controller Configuration

and Status Registers for Data Transactions” on page 219. For more detail on initializing

the PCI Controller Configuration and Status Registers, see “Initializing the PCI

Controller Configuration Registers” on page 222.)

After the local Configuration and Status Register and PCI Controller Configuration and

Status Registers have been initialized, the remainder of the PCI bus is ready to be

configured by the hosting IXP42X product line and IXC1100 control plane processors.

The IXP42X product line and IXC1100 control plane processors will now begin to initiate

configuration cycles to all of the potential devices on the PCI bus.

The order and nature in which the devices are learned is up to the individual

application. However, one bit that must be configured prior to initiating PCI

Configuration Cycles with the IXP42X product line and IXC1100 control plane

processors. Bit 2 of the PCI Control Register/Status (PCI_SRCR) Register must be set

to logic 1 using the methods described in “Initializing the PCI Controller Configuration

Registers” on page 222. The setting of bit 2 to logic 1 enables PCI bus-mastering

capability.

Two types of PCI Configuration Cycles can be generated using the IXP42X product line

and IXC1100 control plane processors: Type 0 and Type 1 Configuration Cycles. Type 0

Configuration Cycles are use to communicate to a PCI device which is contained on the

same local segment that the generator of the Configuration Cycles. Type 1

Configuration Cycles are use to communicate to a PCI device which is contained on

another segment of the PCI bus other than the PCI bus segment that is generating the

Configuration Cycles, i.e., a segment on the other side of a PCI bridge.

A PCI bus can have up to 32 devices (logically but there are loading restrictions that

limit this number) per segment and up to 256 segments. Figure 33 shows the address

makeup for Type 0 PCI bus configuration cycles and Figure 34 shows the address

makeup Type 1 PCI bus configuration cycles.

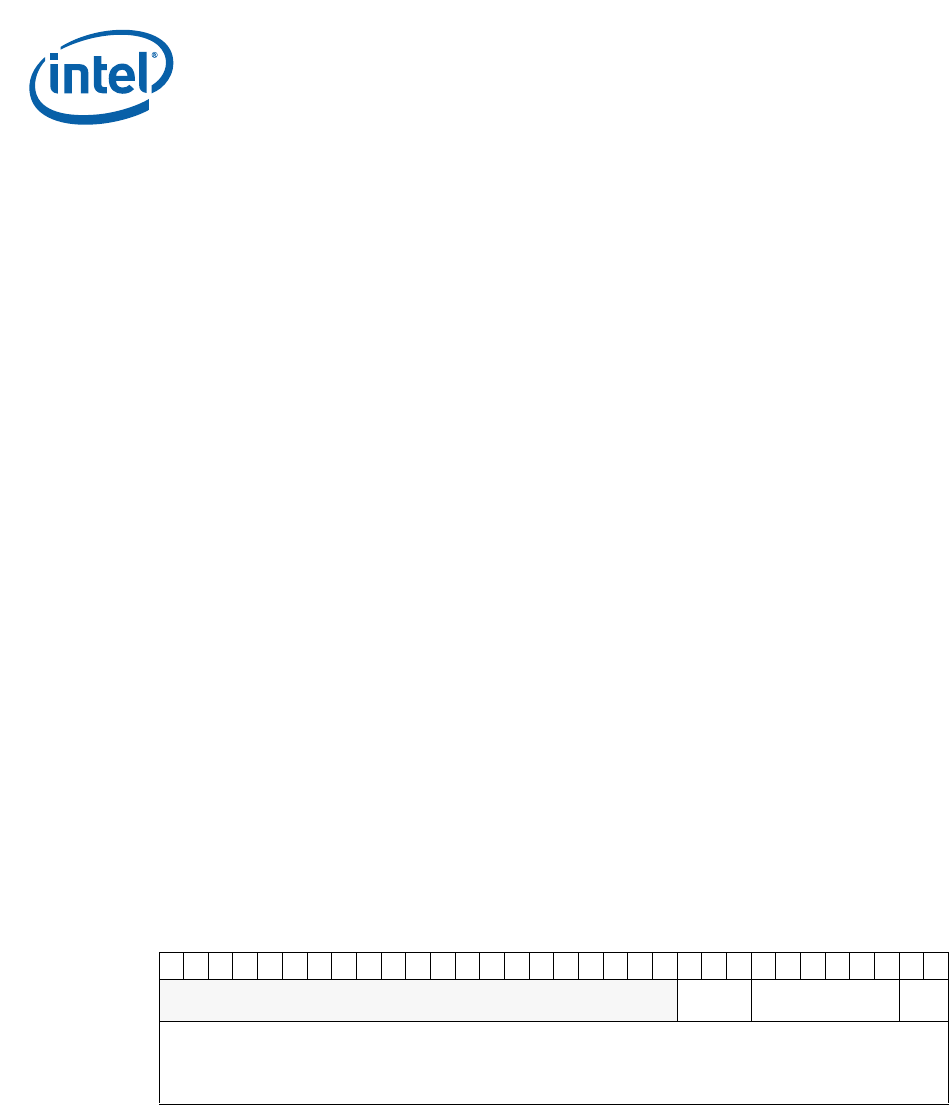

Figure 33. Type 0 Configuration Address Phase

31

20

11

10

8

7

2

1

0

(Reserved)

Function

Number

Register Number

Cycle

Type

Cycle Type=00 for Type 0 Configuration Cycles

Register Number=Defines one of 64 PCI defined 32-bit registers

Function Number=Decodes 1 of 8 possible functions per PCI device (only Function 0 supported for the IXP42X

product line and IXC1100 control plane processors)