Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 457

High-Speed Serial Interfaces—Intel

®

IXP42X product line and IXC1100 control plane

processors

17.6 HSS Supported Framing Protocols

The following sections provide an overview of some Framing Protocols supported by

each of the two IXP421, IXP423 and IXP425 network processors’ HSS interfaces in

addition to the recommended HSS interface setting for each protocol that are

configured using the IxHssAcc API defined in the Intel

®

IXP400 Software Programmer’s

Guide.

17.6.1 T1

T1 is a serial data stream operating at 1.544 MHz. The stream is composed of frames of

which there are 8000 a second. Each frame consists of 1 frame bit and 24 timeslots,

each timeslot is a byte in size. As there are 24 timeslots per frame, T1 can carry 24

channels.

Figure 86 and Figure 87 illustrate a typical T1 frame with an active high frame sync

(level) and a positive edge clock for generating or sampling data. The HSS clock and

frame pulse can be programmed to be either HSS outputs or HSS inputs. An offset can

be programmed indicating when the TX frame is to be transmitted. The Polarity of the

received data and the level of the frame can also be programmed using the IxHssAcc

API.

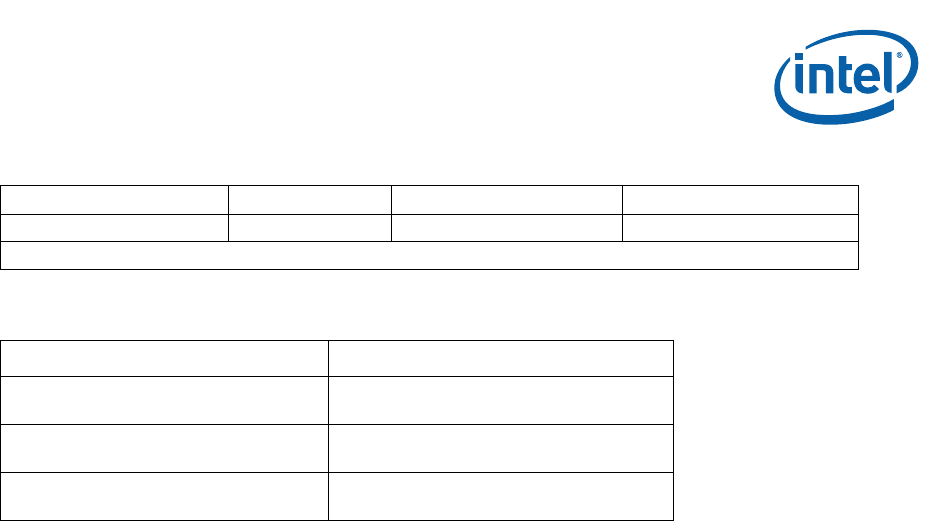

4.096 MHz 512 62.496 -60.0096

8.192 MHz 1024 62.49624 -60.0096

Note: PPM frame length error is calculated from ideal frame frequency.

Table 159. Jitter Definitions

Jitter Type Jitter Definition

Period Jitter (Pj):

Cycle-to-Cycle Jitter (Cj):

Wander-or-Accumulated Jitter (Aj):

Table 158. HSS Frame Output Characterization

averag

e

ii

PeriodPeriodPj −=

)()(

)()1()( iii

PjPjCj −=

+

∑

=

i

i

PjAj

)(