Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Asynchronous

Receiver Transceiver (UART)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

346 Order Number: 252480-006US

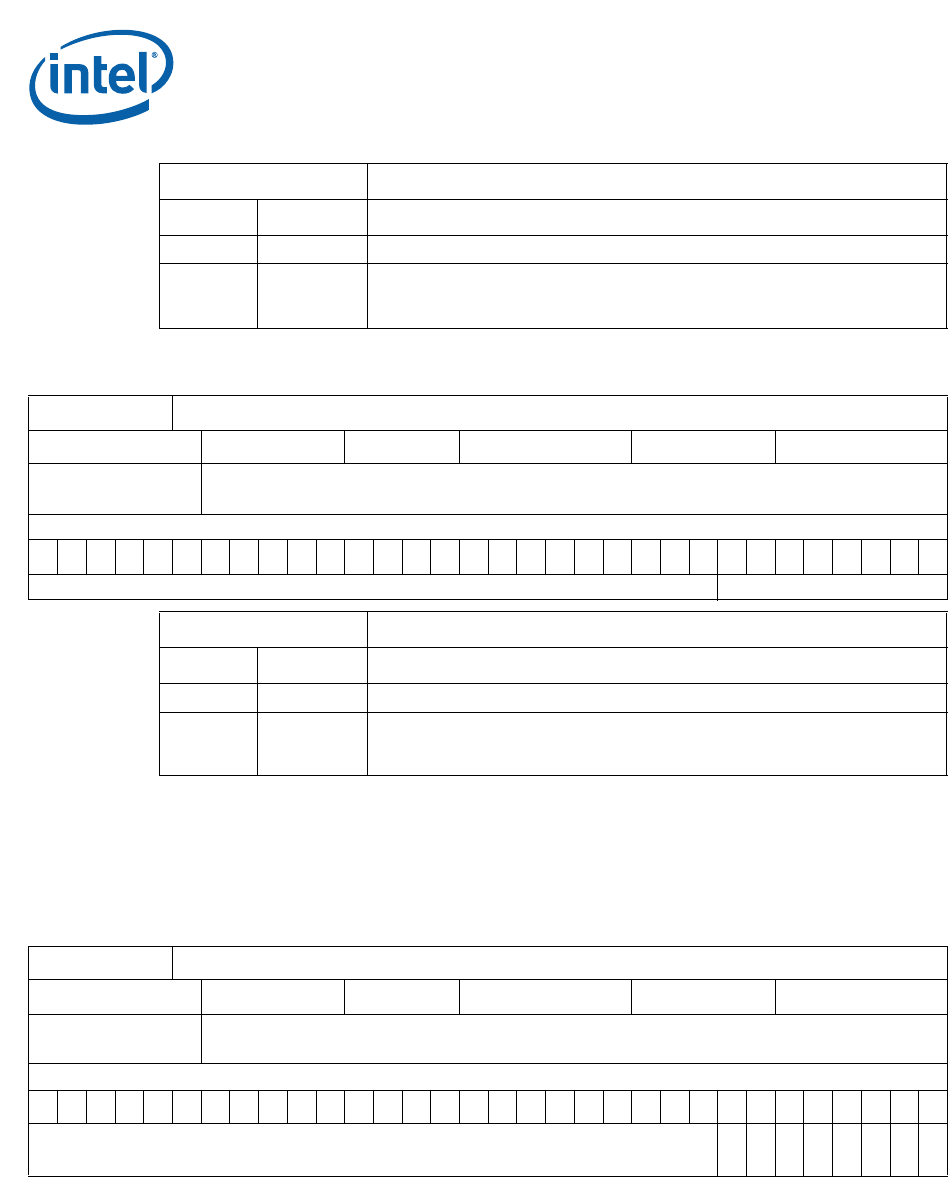

10.4.4 Divisor Latch High Register

10.4.5 Interrupt Enable Register

The DLAB bit in the Line-Control Register must be set to logic 0 to access this register.

Note: All interrupts will be masked, if OUT2 = 0 of the Modem Control Register (see “Modem

Control Register” on page 352). If Interrupts need to be enabled, set OUT2 = 1 of the

Modem Control Register.

Register DLL

Bits Name Description

31:8 (Reserved)

7:0 DLL

Lower byte of compare-value used by the baud rate generator.

The DLAB bit in the Line Control Register must be set to logic 1 to access this

register.

Register Name: DLH

Hex Offset Address: 0xC800 0004 Reset Hex Value: 0x00000000

Register

Description:

Divisor Latch High Register

Access: Read/Write.

31 87 0

(Reserved) DLH

Register

DLH

Bits Name Description

31:8 (Reserved)

7:0 DLH

Upper byte of compare-value used by the baud-rate generator.

The DLAB bit in the Line Control Register must be set to logic 1 to access this

register.

Register Name: IER

Hex Offset Address: 0xC800 0004 Reset Hex Value: 0x00000000

Register

Description:

Interrupt Enable Register

Access: See below.

31 876543210

(Reserved)

DMAE

UUE

NRZE

RTOIE

RIE

RLSE

TIE

RAVIE