Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 377

Internal Bus Performance Monitoring Unit (IBPMU)—Intel

®

IXP42X product line and IXC1100

control plane processors

11.2.2 Monitored SDRAM Events

Selecting SDRAM mode enables the programmable event counters to monitor SDRAM

hits and misses. All programmable event counters are clocked at 133 MHz frequency.

11.2.3 Cycle Count

In all but halt mode, Programmable Event Counter 7 can be configured to count

133-MHz bus-clock cycles. The ability to count the 133-MHz bus-clock cycles is referred

to as “cycle count.”

The cycle count allows an accurate measurement of the duration of the test to be

made. The cycle count is reset and started each time a value is written to the ESR and

the mode is not halt. When HALT mode is selected the counter stops, preserving its last

value. If the count overflows the PEC7, the overflow interrupt is set.

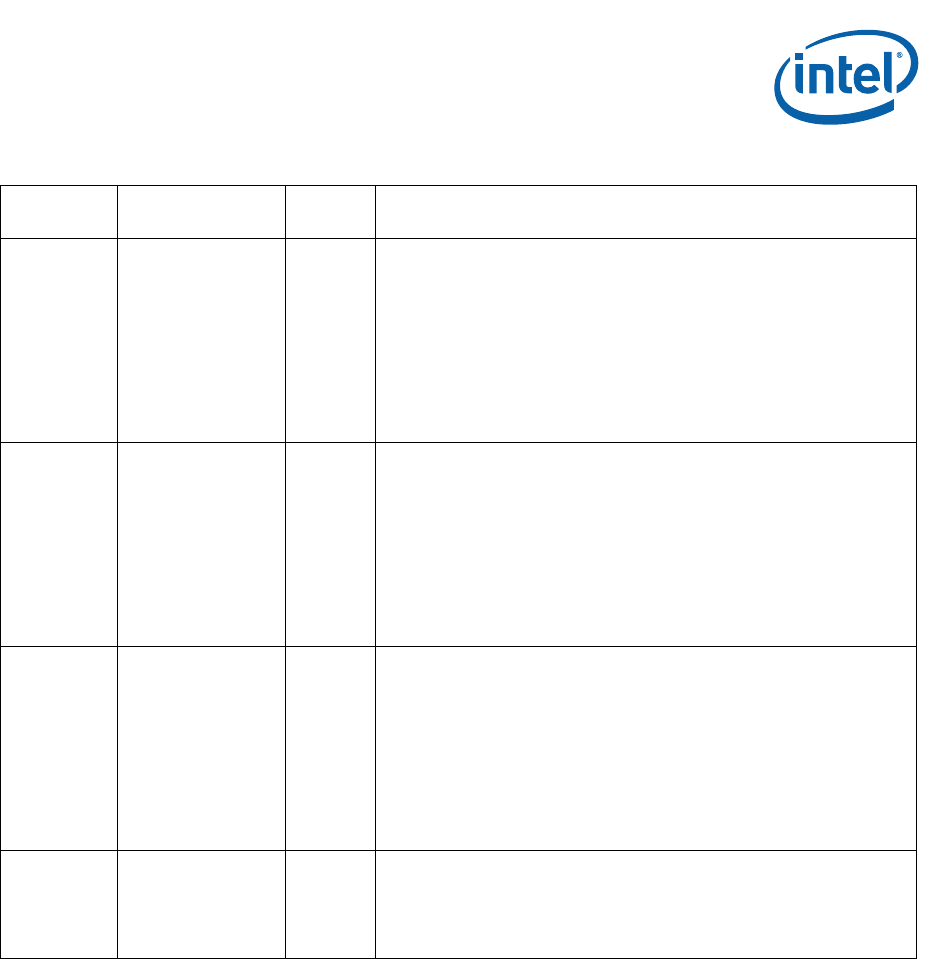

MstrX_Grant

North:

•WAN/Voice NPE

•Ethernet NPE A

•Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Occur

Monitors the number of times the master is granted the bus. It increments

the counter when the master is the bus initiator.

The counter is incremented once for every new transaction. For multi-cycle

transactions, the counter increments once on the first cycle.

MstrX_Xfer

North:

•WAN/Voice NPE

•Ethernet NPE A

•Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Occur

Increments the counter every time that the master initiates a transaction

on the bus.

This event primitive can be used in conjunction with another event

primitive, MstrX_Retry, to calculate the effectiveness of transactions

initiated on the AHB Bus by the master (i.e., percentage transactions

initiated by the master that are not retried.).

MstrX_Retry

North:

•WAN/Voice NPE

•Ethernet NPE A

•Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Occur

Increments the counter every time that a transaction initiated by the

master is responded to with a retry by the target.

SlaveX_Split

North:

• AHB/AHB Bridge

South:

• PCI Bus

• Expansion Bus

Occur Counts the number of times that SlaveX claims a Split Transaction.

Table 142. North and South Modes Event Descriptions (Sheet 2 of 2)

Event

Bus

Components

Type Description