Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

244 Order Number: 252480-006US

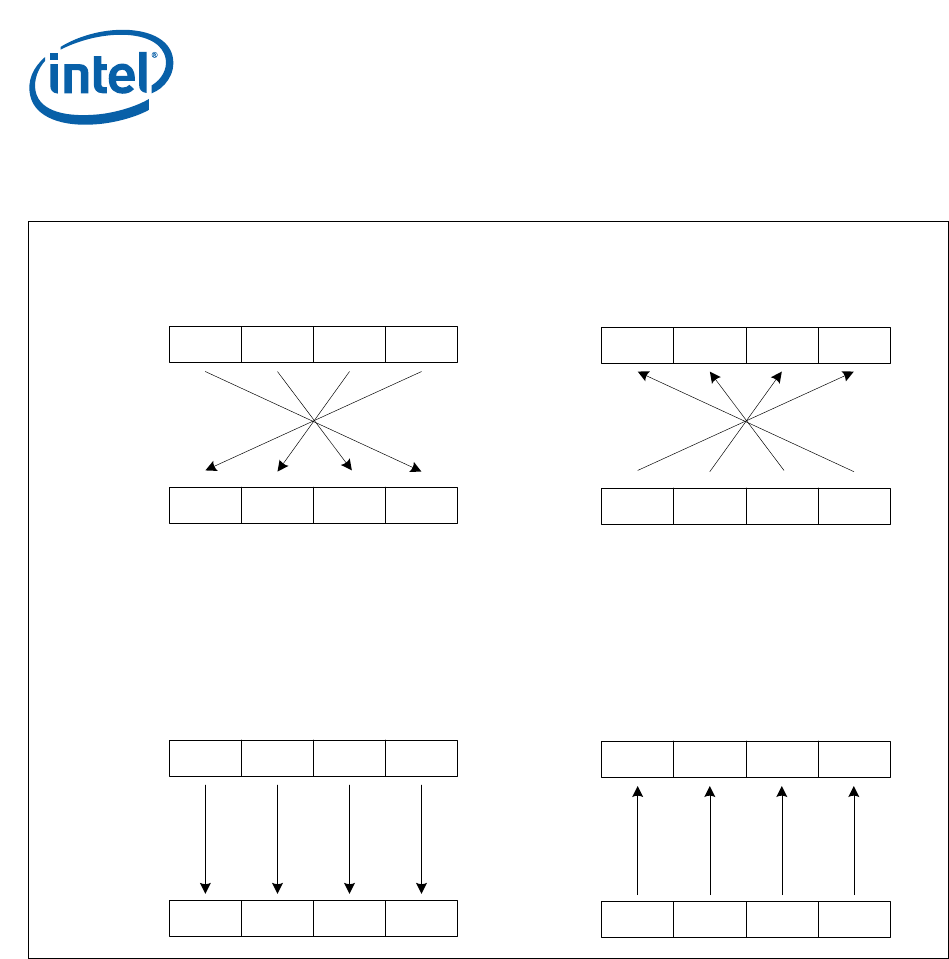

In a similar fashion — as described for PCI Target accesses directed towards the

IXP42X product line and IXC1100 control plane processors — bit 2 (AHB Memory

Mapped Byte Swap) of the PCI Controller Control and Status Register (PCI_CSR)

controls byte-lane routing when an AHB agent accesses an external PCI device using

memory-mapped accesses (0x48000000 to 0x4BFFFFFF). Figure 49 and Figure 50

illustrate the data routing when the AHB is configured as big endian and little-endian

modes.

Figure 48. Byte Lane Routing During PCI Target Accesses of the AHB –

AHB Configured as a Little-Endian Bus

31

24

Write,

pci_csr.PDS = 1

AHB Data

3

2

1

0

23

16

15

8

7

0

31

24

11 10

01

00

23

16

15

8

7

0

31

24

3 2

1

0

23

16

15

8

7

0

31

24

11 10

01

00

23

16

15

8

7

0

AHB Data

PCI Data PCI Data

Read,

pci_csr.PDS = 1

31

24

Write,

pci_csr.PDS = 0

AHB Data

3

2

1

0

23

16

15

8

7

0

31

24

11 10

01

00

23

16

15

8

7

0

31

24

3 2

1

0

23

16

15

8

7

0

31

24

11 10

01

00

23

16

15

8

7

0

AHB Data

PCI Data PCI Data

Read,

pci_csr.PDS = 0