Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

78 Order Number: 252480-006US

The mini-data cache attribute bits, in the Auxiliary Control Register, are used to control

the allocation policy for the mini-data cache and whether it will use write-back caching

or write-through caching.

The configuration of the mini-data cache should be setup before any data access is

made that may be cached in the mini-data cache. Once data is cached, software must

ensure that the mini-data cache has been cleaned and invalidated before the mini-data

cache attributes can be changed.

11 Read / Write

Branch Target Buffer Enable (Z)

0 = Disabled

1 = Enabled

10 Read-as-Zero / Write-as-Zero Reserved

9Read / Write

ROM Protection (R)

This selects the access checks performed by the memory

management unit. See the ARM* Architecture Reference

Manual for more information.

8Read / Write

System Protection (S)

This selects the access checks performed by the memory

management unit. See the ARM* Architecture Reference

Manual for more information.

7Read / Write

Big/Little Endian (B)

0 = Little-endian operation

1 = Big-endian operation

6:3 Read-as-One / Write-as-One = 0b1111

2 Read / Write

Data cache enable/disable (C)

0 = Disabled

1 = Enabled

1Read / Write

Alignment fault enable/disable (A)

0 = Disabled

1 = Enabled

0Read / Write

Memory management unit enable/disable (M)

0 = Disabled

1 = Enabled

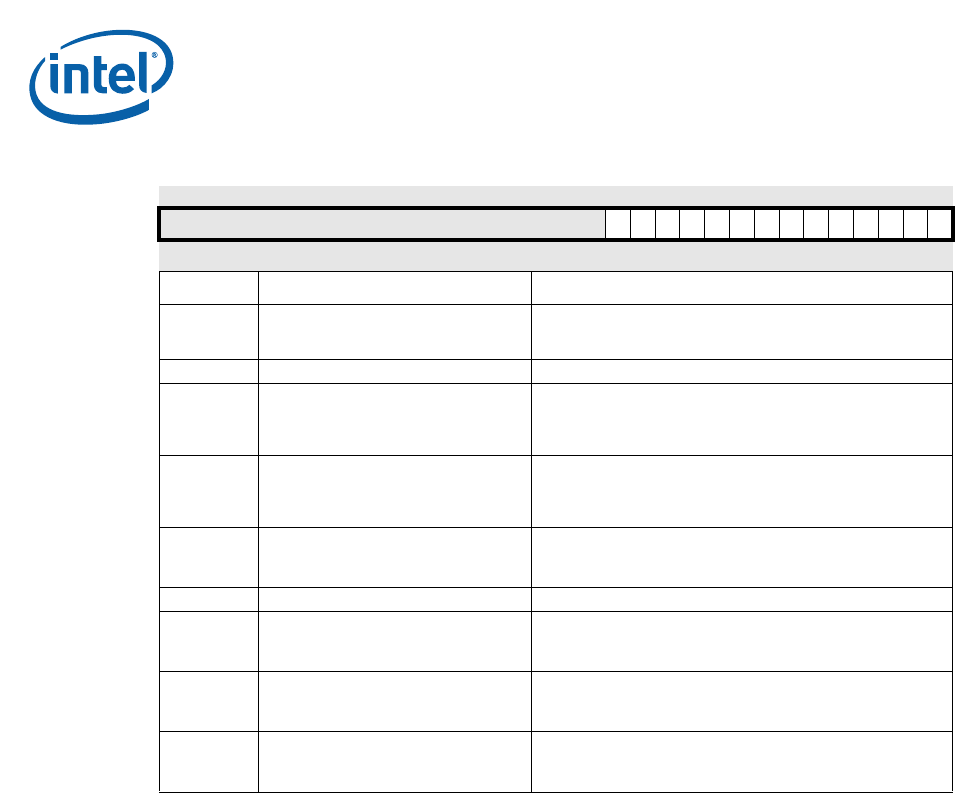

Table 12. ARM

*

Control Register (Sheet 2 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

VIZ0RSB1111CAM

reset value: writeable bits set to 0

Bits Access Description