Intel

®

IXP42X product line and IXC1100 control plane processors—General Purpose Input/

Output (GPIO)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

394 Order Number: 252480-006US

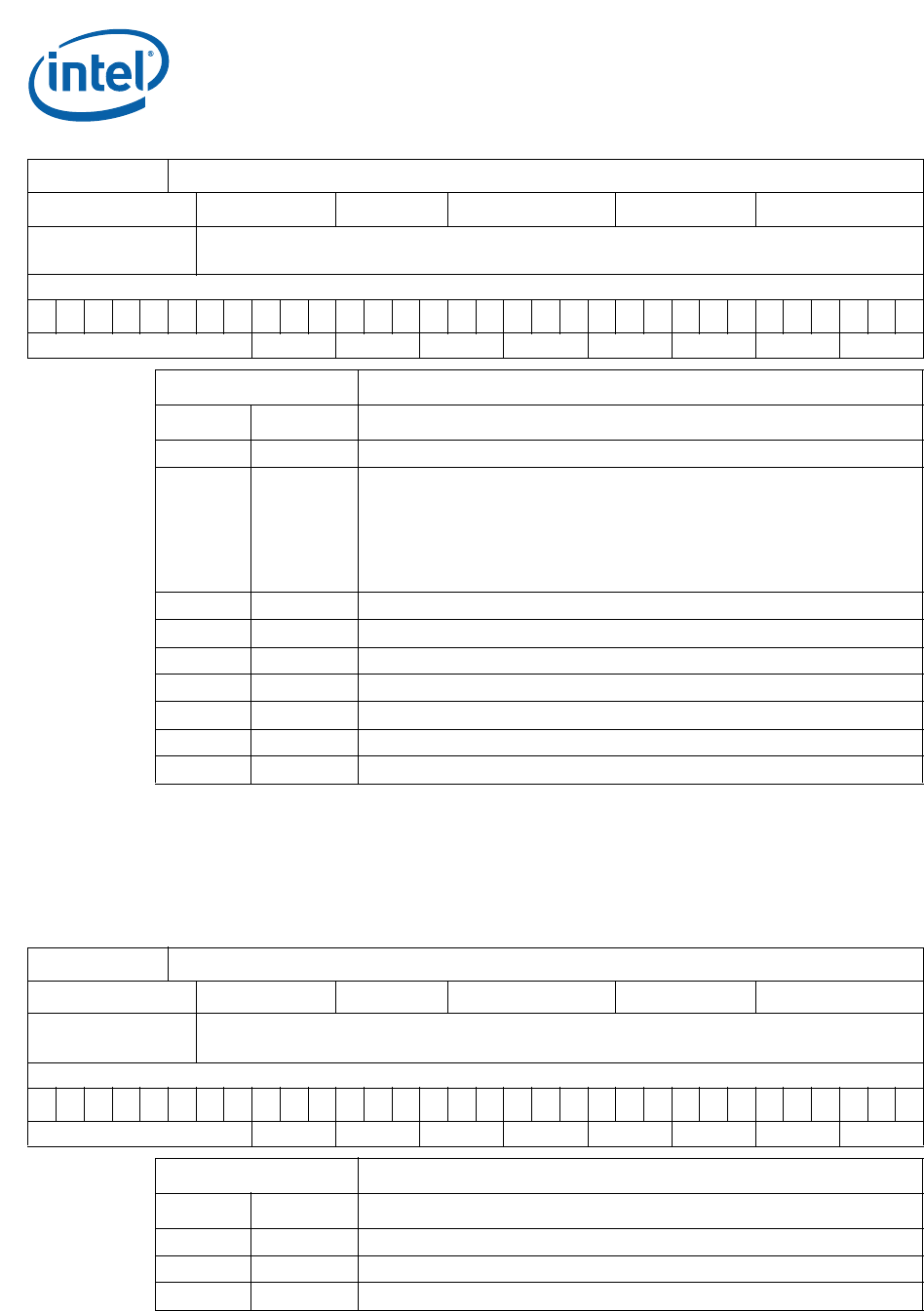

12.4.6 GPIO Interrupt Type Register 2

(GPIT2R)

This register describes how to interpret GPIO[15:8] as interrupts — either level or edge

— along with high, low, rising, falling, and transitional. Three bits describe each GPIO

pin, as described in the following table.

Register Name: GPIT1R

Hex Offset Address: 0xC800 4010 Reset Hex Value: 0x00000000

Register

Description:

This register is used to control interrupt type for GPIO 7:0.

Access: See below.

31 24 23 21 20 18 17 15 14 12 11 9 8 6 5 3 2 0

(Reserved) GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0

Register

GPIT1R

Bits Name Description

31:24 Not used. Ignored on writes and driven logic ‘0’ on reads.

23:21 GPIO7

000 = Active High

001 = Active Low

010 = Rising Edge

011 = Falling Edge

1xx = Transitional

Resets to 000 – Active High

20:18 GPIO6 As per GPIO7

17:15 GPIO5 As per GPIO7

14:12 GPIO4 As per GPIO7

11:9 GPIO3 As per GPIO7

8:6 GPIO2 As per GPIO7

5:3 GPIO1 As per GPIO7

2:0 GPIO0 As per GPIO7

Register Name: GPIT2R

Hex Offset Address: 0xC800 4014 Reset Hex Value: 0x00000000

Register

Description:

This register is used to control interrupt type for GPIO 12:8.

Access: Read/Write.

31 24 23 21 20 18 17 15 14 12 11 9 8 6 5 3 2 0

(Reserved) Not used Not used Not used GPIO12 GPIO11 GPIO10 GPIO9 GPIO8

Register

GPIT2R (Sheet 1 of 2)

Bits Name Description

31:24 Not used. Ignored on writes and driven logic ‘0’ on reads.

23:21 GPIO15 Not used.

20:18 GPIO14 Not used.