Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 433

Ethernet MAC A—Intel

®

IXP42X product line and IXC1100 control plane processors

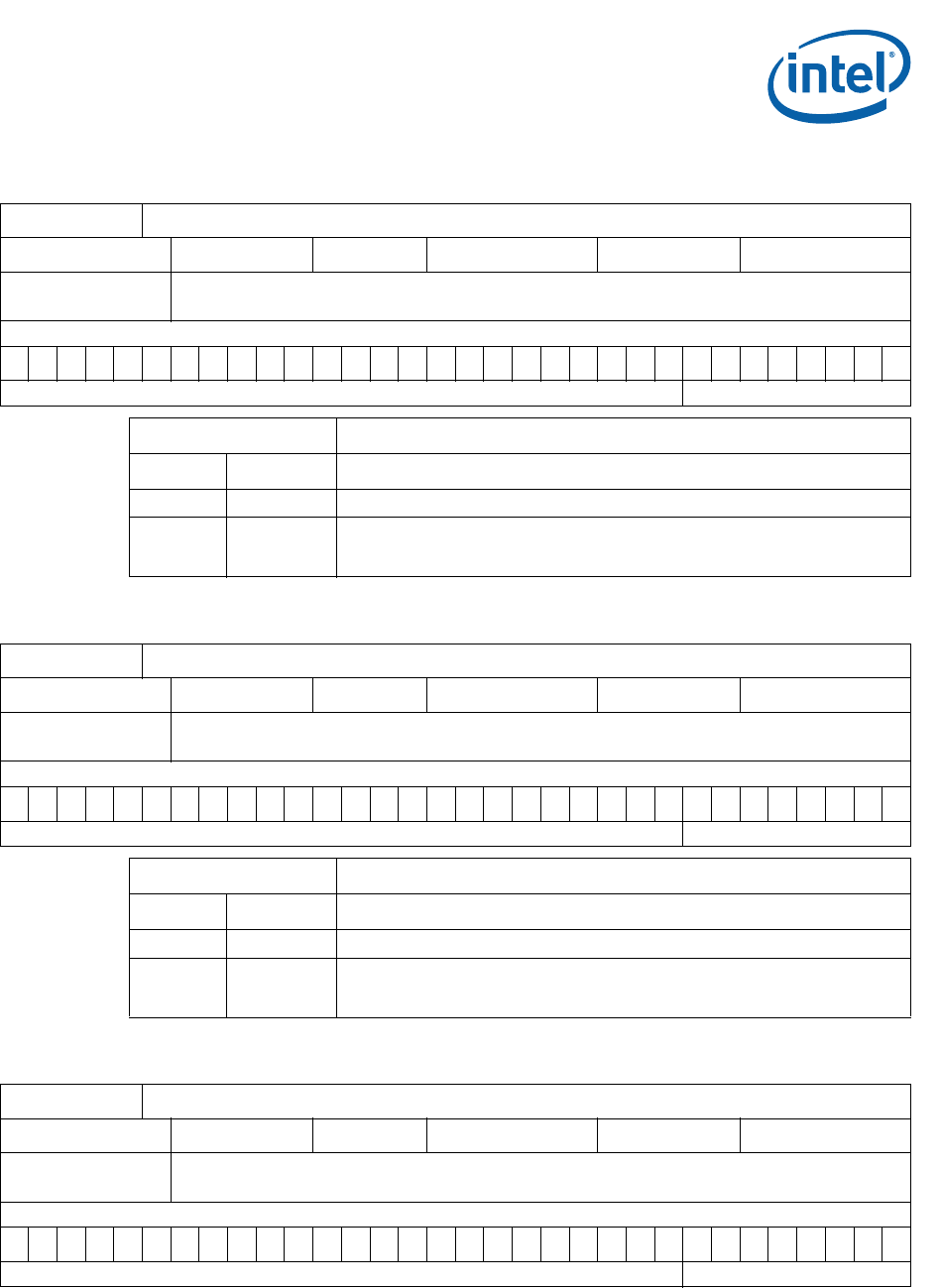

15.2.11 Transmit Two Part Deferral Parameters 1

15.2.12 Transmit Two Part Deferral Parameters 2

15.2.13 Slot Time

Register Name: tx2partdefpars1

Hex Offset Address: 0xC8009060 Reset Hex Value: 0x00000000

Register

Description:

Transmit Two Part Deferral Parameters Register 1.

Access: Read/Write.

31 87 0

(Reserved) First Deferral Period

Register tx2partdefpars1

Bits Name Description

31:8 (Reserved)

7:0

First Deferral

Period

Number of transmit clock cycles (tx_clk) in the first deferral period minus three,

when two-part deferral is used for transmission (Transmit Control 1[5] = 1) and

half-duplex mode.

Register Name: tx2partdefpars2

Hex Offset Address: 0xC8009064 Reset Hex Value: 0x00000000

Register

Description:

Transmit Two Part Deferral Parameters Register 2.

Access: Read/Write.

31 87 0

(Reserved) Second Deferral Period

Register tx2partdefpars2

Bits Name Description

31:8 (Reserved)

7:0

Second

Deferral

Period

Number of transmit clock cycles (tx_clk) in the second deferral period minus

three, when two-part deferral is used for transmission (Transmit Control 1[5] =

1) and half-duplex mode.

Register Name: slottime

Hex Offset Address: 0xC8009070 Reset Hex Value: 0x00000000

Register

Description:

Slot Time Register

Access: Read/Write.

31 87 0

(Reserved) Slot Time