Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 117

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

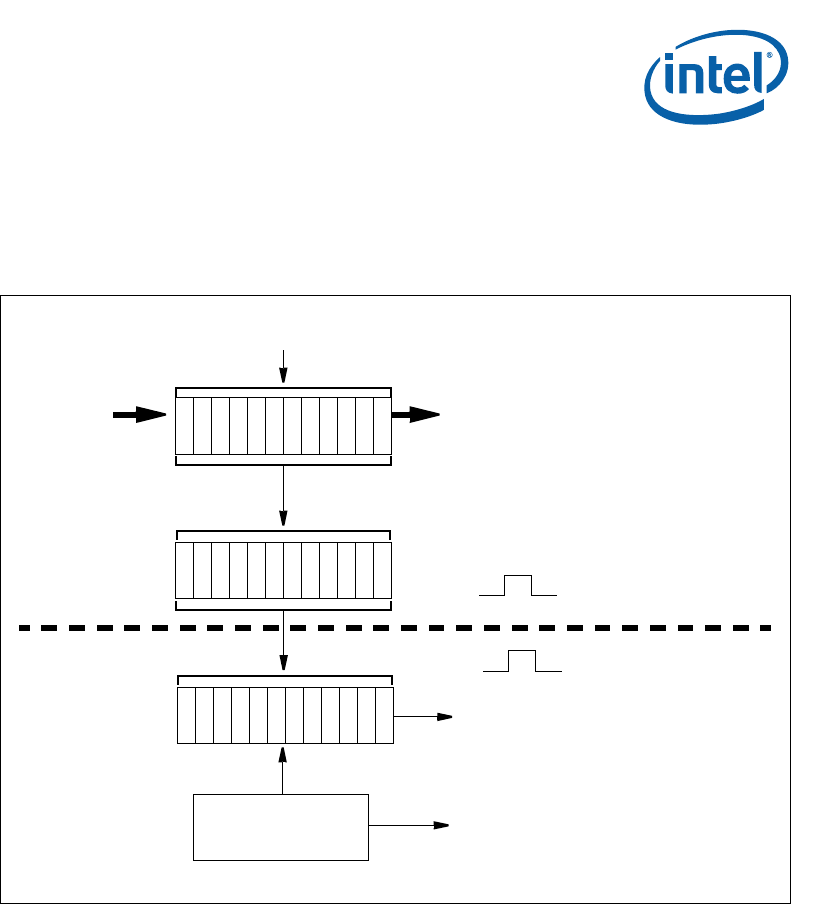

3.6.14.2 LDIC JTAG Data Register

The LDIC JTAG Data Register is selected when the LDIC JTAG instruction is in the JTAG

IR. An external host can load and invalidate lines in the instruction cache through this

data register.

The data loaded into LDIC_SR1 during a Capture_DR is unpredictable.

All LDIC functions and data consists of 33-bit packets which are scanned into LDIC_SR1

during the Shift_DR state.

Update_DR parallel loads LDIC_SR1 into LDIC_REG which is then synchronized with the

IXP42X product line and IXC1100 control plane processors’ clock and loaded into the

LDIC_SR2. Once data is loaded into LDIC_SR2, the LDIC State Machine turns on and

serially shifts the contents if LDIC_SR2 to the instruction cache.

Note that there is a delay from the time of the Update_DR to the time the entire

contents of LDIC_SR2 have been shifted to the instruction cache. Removing the LDIC

JTAG instruction from the JTAG IR before the entire contents of LDIC_SR2 are sent to

the instruction cache, will result in unpredictable behavior. Therefore, following the

Update_DR for the last LDIC packet, the LDIC instruction must remain in the JTAG IR

for a minimum of 15 TCKs. This ensures the last packet is correctly sent to the

instruction cache.

Figure 24. LDIC JTAG Data Register Hardware

TDOTDI

Capture_DR

Update_DR

12332

TCK

Core CLK

0

12

32

0

unpredictable

LDIC_SR1

To Instruction Cache

LDIC_REG

12

32

0

LDIC_SR2

LDIC

State Machine