Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 119

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

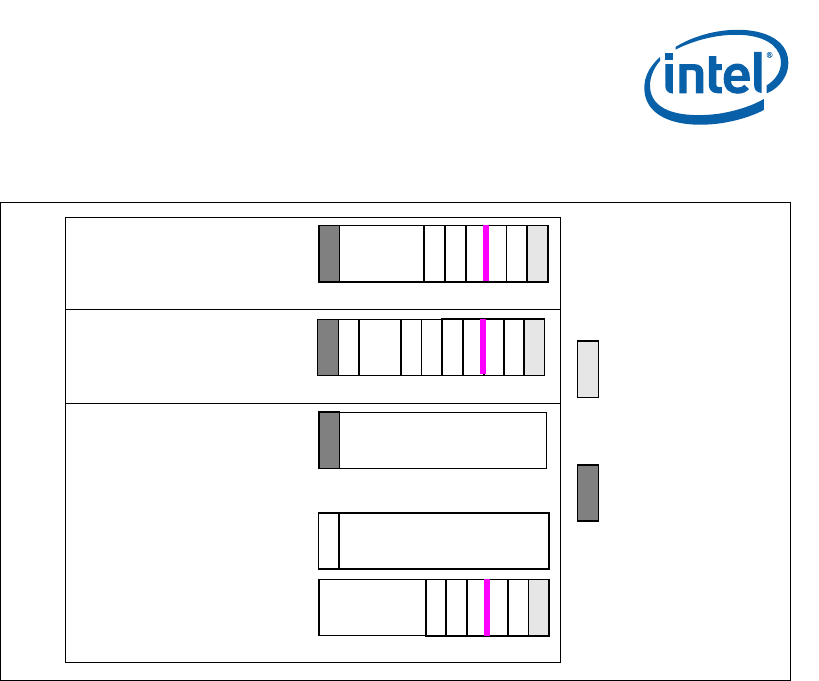

All packets are 33 bits in length. Bits [2:0] of the first packet specify the function to

execute. For functions that require an address, bits[32:6] of the first packet specify an

eight-word aligned address (Packet1[32:6] = VA[31:5]). For Load Main IC and Load

Mini IC, eight additional data packets are used to specify eight ARM instructions to be

loaded into the target instruction cache. Bits[31:0] of the data packets contain the data

to download. Bit[32] of each data packet is the value of the parity for the data in that

packet.

As shown in Figure 25, the first bit shifted in TDI is bit 0 of the first packet. After each

33-bit packet, the host must take the JTAG state machine into the Update_DR state.

After the host does an Update_DR and returns the JTAG state machine back to the

Shift_DR state, the host can immediately begin shifting in the next 33-bit packet.

3.6.14.4 Loading IC During Reset

Code can be downloaded into the instruction cache through JTAG during a processor

reset. This feature is used during software debug to download the debug handler prior

to starting an application program. The downloaded handler can then intercept the

reset vector and do any necessary setup before the application code executes

In general, any code downloaded into the instruction cache through JTAG, must be

downloaded to addresses that are not already valid in the instruction cache. Failure to

meet this requirement will result in unpredictable behavior by the processor. During a

processor reset, the instruction cache is typically invalidated, with the exception of the

following modes:

• LDIC mode — Active when LDIC JTAG instruction is loaded in the JTAG IR; prevents

the mini instruction cache and the main instruction cache from being invalidated

during reset.

• HALT mode — Active when the Halt Mode bit is set in the DCSR; prevents only the

mini instruction cache from being invalidated; main instruction cache is invalidated

by reset.

Figure 25. Format of LDIC Cache Functions

25

00

31

Invalidate IC Line

x0xx

. . .

Invalidate Mini IC

VA[31:5]

Load Main IC

VA[31:5]

.

.

.

Data Word 0

Data Word 7

Load Mini IC

and

(CMD = 0b010)

(CMD = 0b011)

- indicates first

- indicates last

bit shifted in

bit shifted in

0 00

000 0

0

0

0 0

CMD

32

0

1

2531 032

2531 032

P

P