Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

252 Order Number: 252480-006US

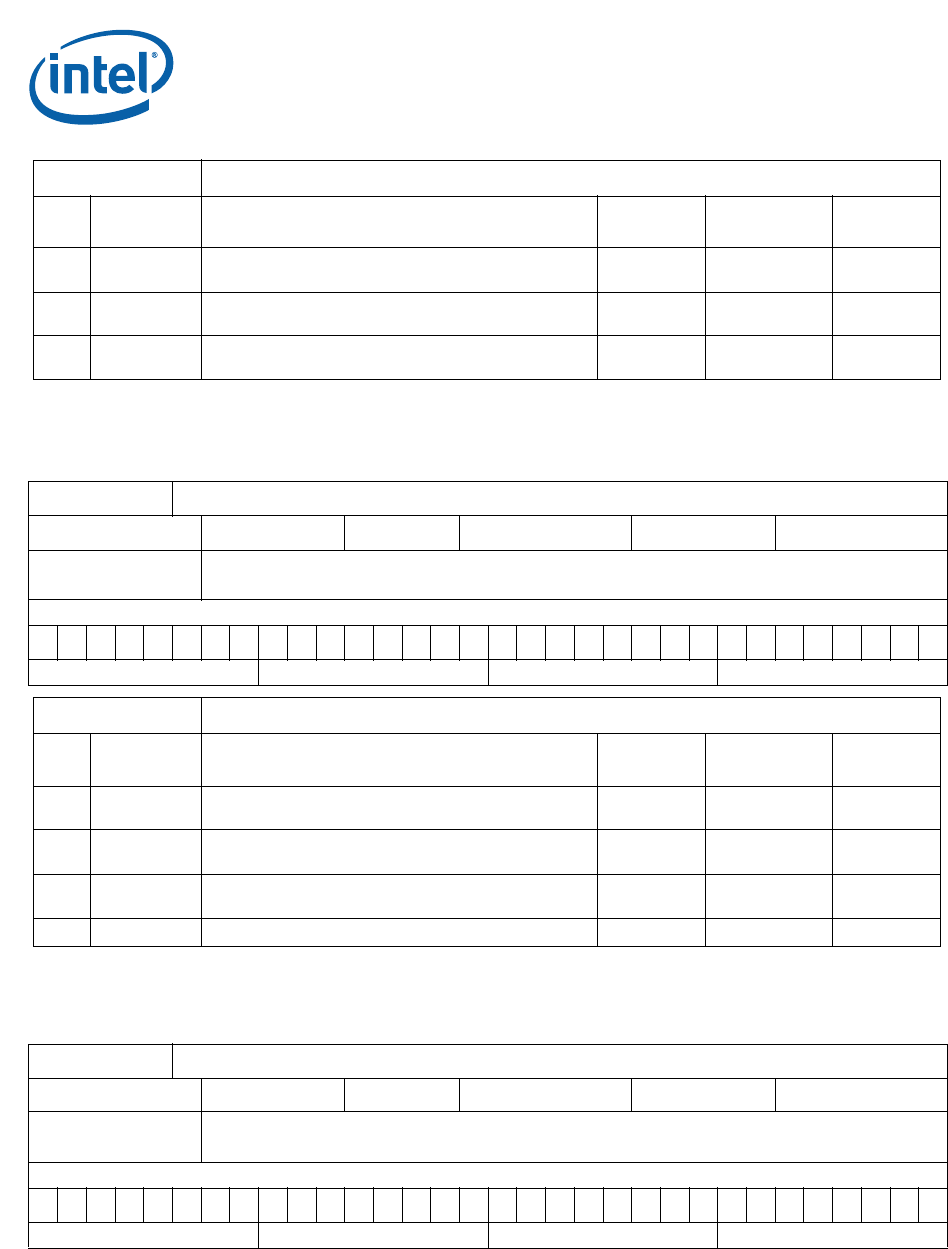

6.14.1.3 Class Code/Revision ID Register

(PCI_CCRID)

6.14.1.4 BIST/Header Type/Latency Timer/Cache Line Register

(PCI_BHLC)

2BME

Bus Master Enable. When set, enables this device to

act as a bus Master.

0RWRW

1MAE

Memory Access Enable. When set to a 1, enables

memory accesses as a target.

0RWRW

0IOAE

I/O Access Enable. When set to a 1, enables I/O

accesses as a target.

0RWRW

Register Name: PCI_CCRID

Hex Offset Address: 0x08 Reset Hex Value: 0x0B400000

Register

Description:

Provides Class Code and Revision ID values as specified in the PCI 2.2 Local Bus Specification.

Access: See below.

31 24 23 16 15 8 7 0

Class Code Sub-Class Code Interface RevisionID

Register

PCI_CCRID

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2

4

Class Code

Class/Sub-Class identifier for the device as defined in

the PCI specification. 0x0b = processor

0x0b RO RW

23:1

6

Sub-Class

Sub-Class identifier for Class Code 0x0b. 0x40 = co-

processor

0x40 RO RW

15:8 Interface

Programming Interface code. Always 0x00 for this

class.

0x00 RO RW

7:0 RevisionID Silicon revision for the device. 0x01 RO RW

Register Name: PCI_BHLC

Hex Offset Address: 0x0C Reset Hex Value: 0x00000000

Register

Description:

Provides BIST, Header Type, Latency Timer, and Cache Line Size registers as specified in the PCI 2.2

Local Bus Specification.

Access: See below.

31 24 23 16 15 8 7 0

BIST Header Type LatencyTimer CacheLine

Register

PCI_SRCR (Sheet 2 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access