Intel

®

IXP42X product line and IXC1100 control plane processors—High-Speed Serial

Interfaces

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

454 Order Number: 252480-006US

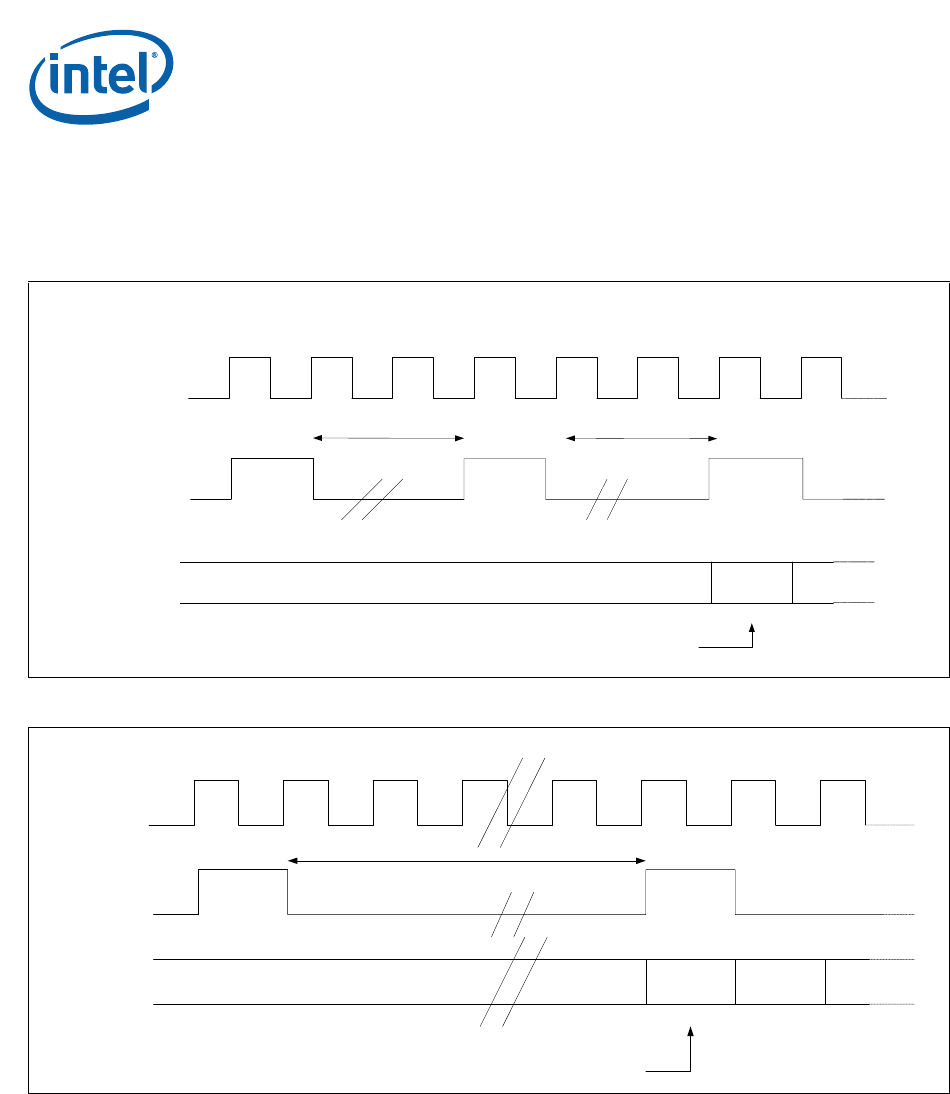

The behavior of the HSS interface is indifferent to the source of the frame-sync pulse.

The frame-sync pulse can be sourced externally or generated internally. Figure 84 and

Figure 85 shows an example of the HSS interfaces obtaining synchronization with no

offset defined.

17.5 HSS Registers and Clock Configuration

There are numerous Control and Status Registers (CSRs) contained within the IXP42X

product line and IXC1100 control plane processors’ NPE/HSS interface that are used to

configure the many unique HSS settings discussed in this manual. The functional

details of these registers are not exposed within any IXP42X product line and IXC1100

control plane processors collateral and are reserved for use by NPE firmware only. The

IxHssAcc API, however, provides indirect access to the these registers to allow the

complete control and configuration of all HSS features enabled by a particular Intel

®

IXP400 Software Release. The Intel

®

IXP400 Software Programmer’s Guide should be

referenced for specific information regarding use of the IxHssAcc API.

Figure 84. Tx Frame-Sync Example (Presuming an Offset of 0)

Figure 85. Rx Frame-Sync Example (Presuming Zero Offset)

hcp_tx_data_out

pads_tx_clock

hcp_tx_frame_out

data data

Data from here will

be transmitted

Correct interval Correct interval

hcp_rx_data

pads_rx_clock

pads_rx_frame

datadatadata

Correct interval

Data from here is processed