Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Asynchronous

Receiver Transceiver (UART)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

338 Order Number: 252480-006US

The Line-Control Register is initialized to hexadecimal 0x00 after reset. The Line-Status

Register is initialized to hexadecimal 0x60 after reset.

10.2.3 Using the Modem Control Signals

The IXP42X product line and IXC1100 control plane processors provide two modem

control signals, the Clear-to-Send input (CTS_N) and the Ready to Send output

(RTS_N).

The Clear-to-Send input signal is sampled by reading the Modem Status Register and

the Ready-to-Send output is controlled by the Modem Control Register. The Modem

Control Register is a 5-bit register that provides control for four modem control signals:

Only one of the four modem-control signals — Ready-to-Send — is replicated to the

external pins of the IXP42X product line and IXC1100 control plane processors. The

three other modem-control signals are only utilized when the UART is being used in

loop-back diagnostic mode. Bit 4 of the Modem-Control Register is the Loop Back Test

Mode bit (LOOP). The Loop Back Test Mode bit provides a local loop-back feature for

diagnostic testing of the UART.

When the Loop Back Test Mode bit is set to logic 1, the following will event will occur:

• The transmitter serial output is set to logic 1 state.

• The receiver serial input is disconnected from the pin.

• The output of the Transmitter Shift Register is “looped back” into the Receiver Shift

Register input.

• The Clear-to-Send input signal is disconnected from the pin

• The Ready-to-Send output signal is forced to logic 1.

• The lower four bits of the Modem Control Register are connected to the upper four

bits of the Modem Status Register

Status register bit mapping, while in loop back mode:

— DTR = 1 forces DSR to a 1

— RTS = 1 forces CTS to a 1

— OUT1 = 1 forces RI to a 1

— OUT2= 1 forces DCD to a 1

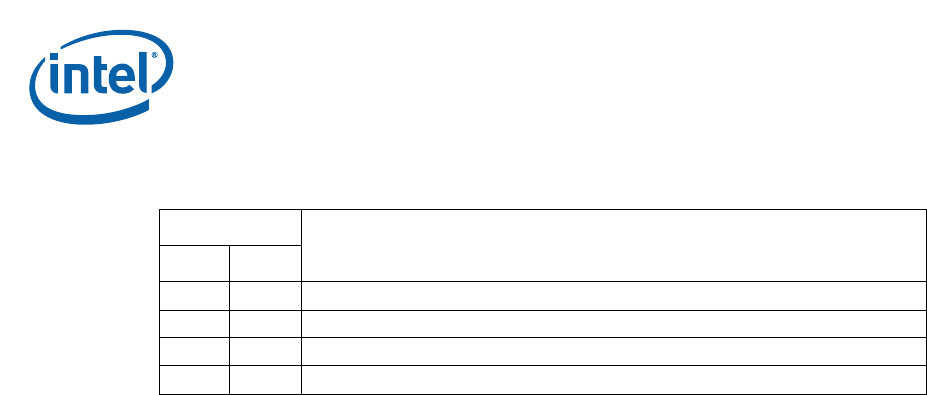

Table 132. UART Word-Length Select Configuration

WLS

Number of Data Bits Contained in Each Transmitted Or Received Character

Bit 1 Bit 0

0 0 5-bit character (default)

0 1 6-bit character

1 0 7-bit character

1 1 8-bit character

• OUT1 • OUT2 • Data Terminal Ready

• Ready-to-Send • Loop-back test control

bit