Intel

®

IXP42X product line and IXC1100 control plane processors—High-Speed Serial

Interfaces

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

448 Order Number: 252480-006US

17.0 High-Speed Serial Interfaces

The functionality supported by the High-Speed Serial (HSS) interfaces are tightly

coupled with the code written on the Network Processor Engine (NPE) core. This

chapter details the full hardware capabilities of the HSS interfaces contained within the

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane

Processor. The features accessible by the user are described in the Intel

®

IXP400

Software Programmer’s Guide and may be a subset of the features described below.

Not all of the Intel

®

IXP42X product line and IXC1100 control plane processors have

this functionality. See Table 154.

The HSS coprocessor enables the IXP42X product line and IXC1100 control plane

processors to communicate in a Time Divisible Multiplexed (TDM) bit serial fashion with

external chips. The HSS interfaces are six-wire, serial interfaces that can operate at

speeds from 512 KHz to 8.192 MHz.

The NPEs core controls each HSS interface. By programming certain parameters to the

HSS interfaces — such as frame length/offset, frame signal polarity, and data

endianness — the interfaces can be configured to support a variety of bit serial

protocols.

For a list of supported protocols, see the Intel

®

IXP400 Software Programmer’s Guide.

17.1 High-Speed Serial Interface Receive Operation

Each High-Speed Serial Interface contains five receive FIFOs and four receive FIFOs

intended for facilitating the use of HDLC. Each is two 32-bit words in length. The four

receive FIFOs are further divided into two buffers, each one 32-bit word in length.

These FIFOs are hardware support added to facilitate the implementation of four HDLC

channels and do not preclude the implementation of more HDLC channels using the

Network Processor Engine core and the HDLC Co-processor connected.

The HSS interface will be filling one buffer while the NPE empties the other buffer. The

fifth receive FIFO is intended for voice-processing support and is four 32-bit words in

length. This receive FIFO is split into two buffers, each buffer two 32-bit words in

length.

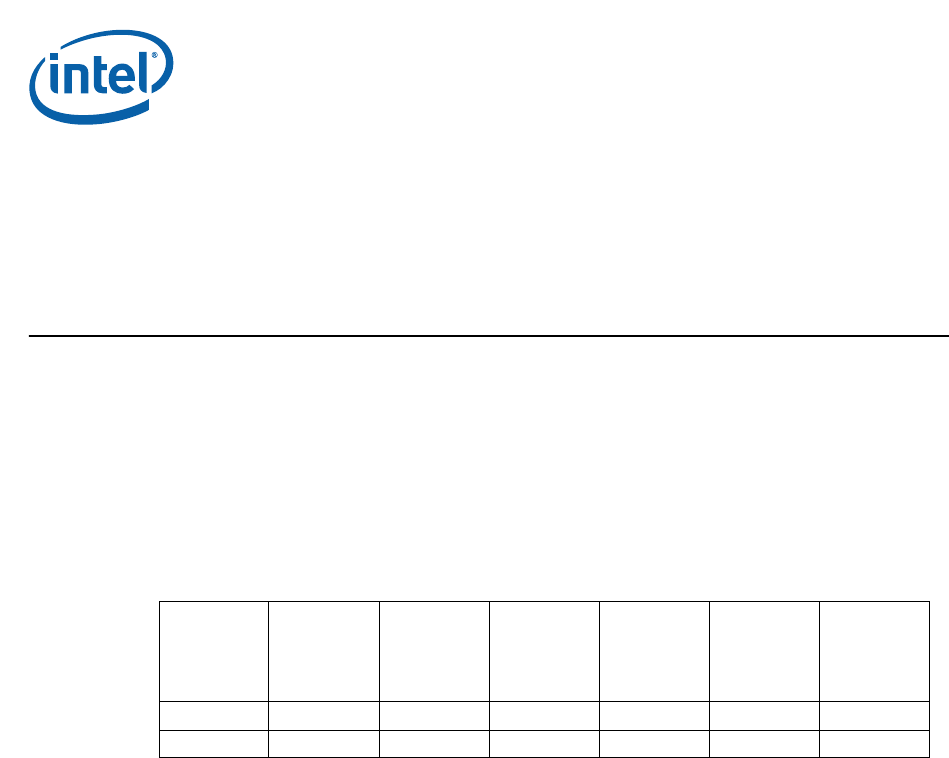

Table 154. Processors with HSS

HSS

Intel

®

IXP425

Network

Processor

B Step

Intel

®

IXP423

Network

Processor

Intel

®

IXP422

Network

Processor

Intel

®

IXP421

Network

Processor

Intel

®

IXP420

Network

Processor

Intel

®

IXC1100

Control

Plane

Processor

HSS 0 X X X

HSS 1 X X X