Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 293

Expansion Bus Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

One of these general-purpose configuration registers is used to capture the value on

the address pins immediately after reset. In the Expansion Bus Interface, 24 address

lines are used to capture this configuration information at the release of reset. When

power up is complete and reset is asserted, the 24 address lines are configured as

inputs. When reset is released (RESET_IN_N), the configuration registers capture the

values contained on the 24 address lines and the 24 address lines become configured

as outputs. The Expansion Bus address signals have internal pull-up resistors of about

50 KΩ. Pull-down resistors may be placed on some of the 24 address lines in order to

select the configuration values at reset. Please refer to Section 8.9.9, “Configuration

Register 0” on page 322 for additional details on particular configuration options.

In normal mode of operation, the 24 bit address bus is used to present the 24 bits of

the address [23:0] used for the requested transaction accompanied by an address latch

enable output signal, (EX_ALE). The address phase normally last one clock cycle in

non-multiplexed mode and two clock cycles in multiplexed mode but may be extended

by one to three clock cycles using the T1 parameter in the Timing and Configuration

Register for the particular Chip Select.

The remaining control signals used by the Expansion Bus Interface can be configured to

operate as Intel, Motorola, or HPI-style control signals. As an example, the write strobe

for Intel mode (EX_WR_N) would be translated to the data strobe (DS_N) when placed

into Motorola mode. Similarly, the Intel-mode read signal (EX_RD_N) would become

read-not-write (R/W_N) when placed in Motorola* mode.

The EX_IOWAIT_N signal is available to be shared by the devices attached to chip 0

through 7, when the chip selects are configured in Intel or Motorola mode of operation.

The EX_IOWAIT_N signal allows an external device to hold off completion of the read

phase of a transaction until the external device can supply the data requested.

Similarly, EX_RDY[3:0] are provided for chip selects 7 through 4, respectively. The

EX_RDY[3:0] signals are used to hold off data transfers when chip selects 7 through 4

are configured in HPI mode. For example when chip select 5 is configured in HPI mode

of operation. Chip select 5 will no longer respond to the EX_IOWAIT_N signal and will

only respond to the EX_RDY_N[1]. All other chip selects will respond to the

EX_IOWAIT_N signal. Chip selects 7 through 4 are the only chip selects that can be

configured in HPI mode of operation.

8.1 Expansion Bus Address Space

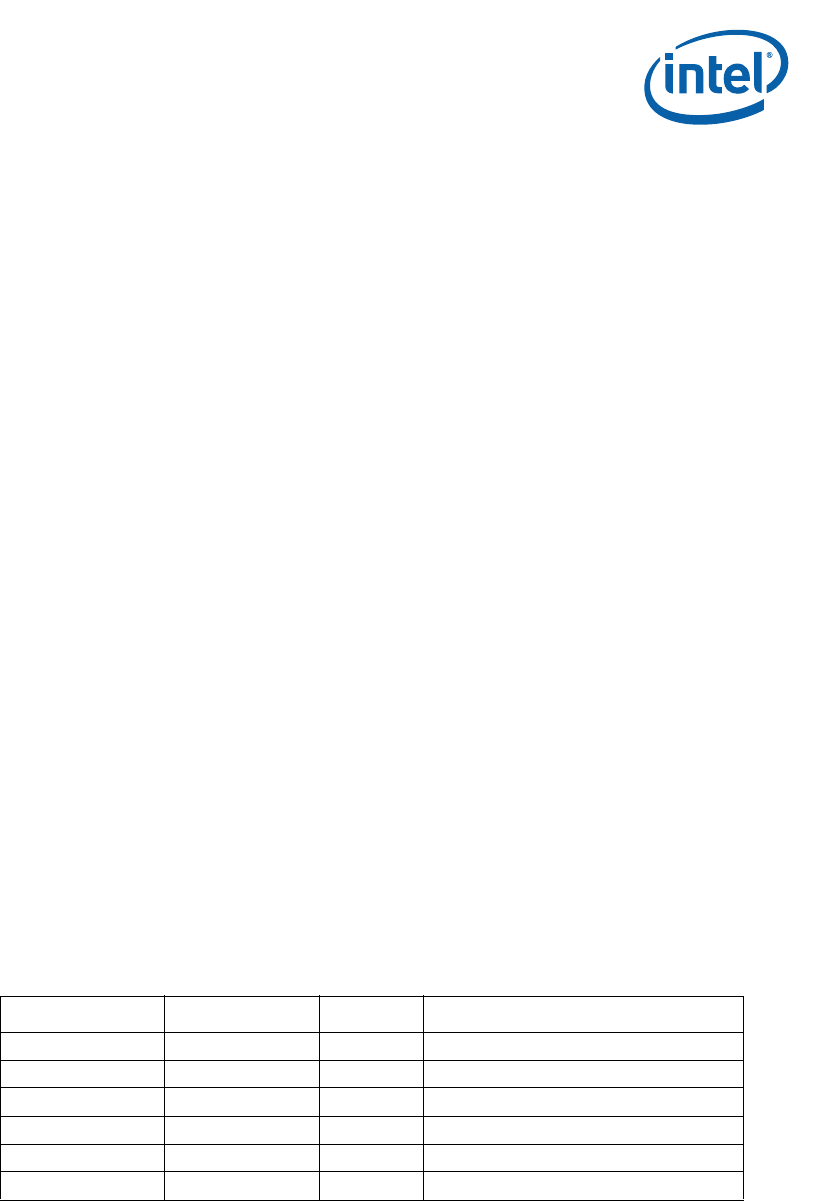

As seen in Table 117, on the South AHB, the lowest 256 Mbytes of address space

(0x00000000 to 0x0FFFFFFF) is overlapped with the SDRAM address space

(0x00000000 to 0x3FFFFFFF). The actual interface that is accessed when the

overlapped region is addressed is configurable based on the value of a configuration

register bit located in the Expansion Bus Controller.

Table 117. Processors’ Trimmed Version of the Memory Map

Start Address End Address Size Use

0000_0000 0FFF_FFFF 256 Mbyte Expansion bus

0000_0000 3FFF_FFFF 1 Gbyte SDRAM

4000_0000 47FF_FFFF 128 Mbyte (Reserved)

4800_0000 4FFF_FFFF 128 Mbyte PCI

5000_0000 5FFF_FFFF 256 Mbyte Expansion bus

6000_0000 63FF_FFFF 64 Mbyte Queue manager