Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 61

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

a cacheable write miss when write allocate is specified by its page attribute. Page

attribute bits determine whether a line gets allocated into the data cache or mini-data

cache.

The mini-data cache is 2 Kbytes in size. The 2-Kbyte mini data cache has 32 sets and is

two-way set associative. Each way of a set contains 32 bytes (one cache line) and one

valid bit. There also exist two dirty bits for every line, one for the lower 16 bytes and

the other one for the upper 16 bytes. When a store hits the cache the dirty bit

associated with it is set. The replacement policy is a round-robin algorithm.

Figure 13, “Mini-Data Cache Organization” on page 62 shows the cache organization

and how the data address is used to access the cache.

The mini-data cache is virtually addressed and virtually tagged and supports the same

caching policies as the data cache. However, lines can’t be locked into the mini-data

cache.

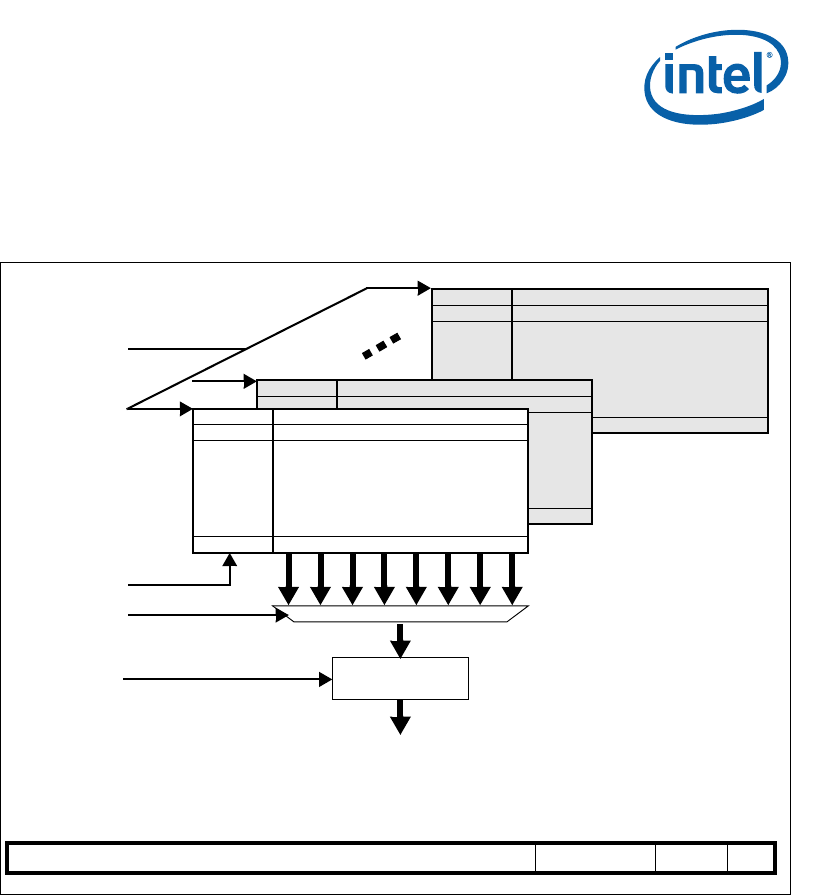

Figure 12. Data Cache Organization

way 0

way 1

way 31

32 bytes (cache line)

Set 31

CAM

DATA

way 0

way 1

way 31

32 bytes (cache line)

Set 1

CAM

DATA

way 0

way 1

way 31

32 bytes (cache line)

Set Index

Set 0

Tag

Data Address (Virtual) — 32-Kbyte Cache

31 109 54 210

Tag Set Index Word Byte

Word Select

CAM

DATA

Data Word

(4 bytes to Destination Register)

Byte Alignment

Sign Extension

Byte Select

This example shows

Set 0 being selected

by the set index.

CAM: Content Addressable Memory

Example: 32-Kbyte cache