Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 429

Ethernet MAC A—Intel

®

IXP42X product line and IXC1100 control plane processors

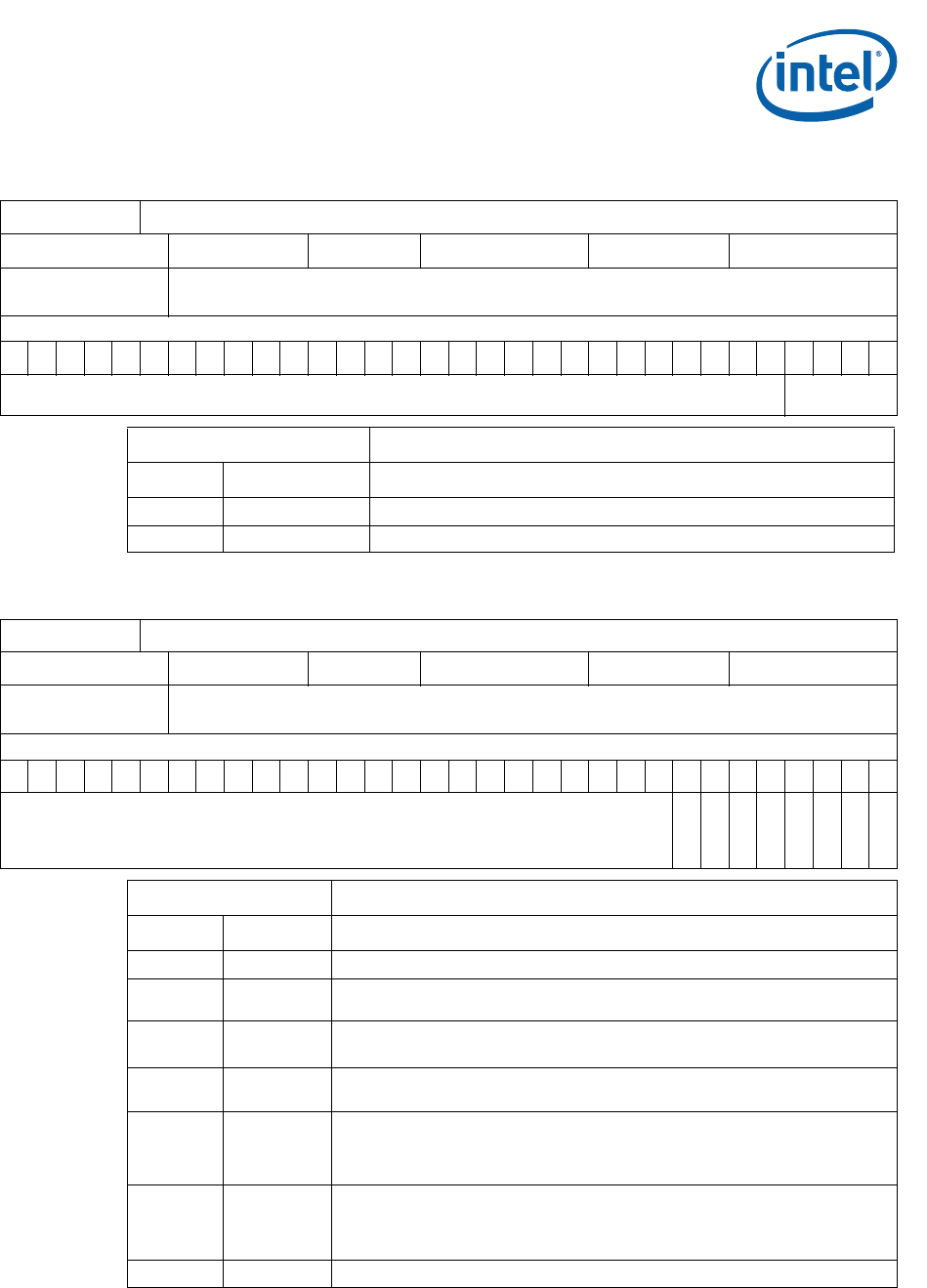

15.2.2 Transmit Control 2

15.2.3 Receive Control 1

Register Name: txcrtl2

Hex Offset Address: 0xC8009004 Reset Hex Value: 0x00000000

Register

Description:

Transmit Control Register Two

Access: Read/Write.

31 43 0

(Reserved)

Maximum

Retries

Register txcrtl2

Bits Name Description

4:31 (Reserved)

3:0 Maximum retries Maximum number of retries for a packet when collisions occur.

Register Name: rxctrl1

Hex Offset Address: 0xC8009010 Reset Hex Value: 0x00000000

Register

Description:

Receive Control Register One

Access: Read/Write.

31 876543210

(Reserved)

BCDIS

RX RP

ADD FILT

LOOP EN

PSE EN

CRC

PAD STRP

RX EN

Register rxcrtl1 (Sheet 1 of 2)

Bits Name Description

31:8 (Reserved)

7

Broadcast

disable

1 = Prevents broadcast packets from being passed to the application logic.

6

Receive runt

packet

1 = Causes runt packets to be passed to the application logic.

0 = Runt packets are dropped.

5

Address filter

enable

1 = Causes address filtering to take place. Non-broadcast packets are only

passed to the application logic if they pass the address filter.

4

Loopback

enable

1 = Causes loop-back operation.

Note: In order for the loop-back operation to operate correctly, the Ethernet

coprocessor requires synchronous and in-phase clocks to be provided

on the rx_clk and tx_clk pins.

3 Pause enable

1 = Enables detection of Pause frames. Upon detecting a pause frame, data

transmission is halted based on the data in the pause frame. The 2-byte data of

the received pause frame indicates the time, as a number of 512 bit times, to

halt the transmission.

2 Send CRC 1 = Causes the CRC data to be sent to the application logic.