Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

86 Order Number: 252480-006US

Example 12. Disallowing access to CP0

3.5.2 CP14 Registers

Table 27 lists the CP14 registers implemented in the Intel XScale processor.

All other registers are reserved in CP14. Reading and writing them yields unpredictable

results.

;; The following code clears bit 0 of the CPAR.

;; This will cause the processor to fault if software

;; attempts to access CP0.

LDR R0, =0x3FFE ; bit 0 is clear

MCR P15, 0, R0, C15, C1, 0 ; move to CPAR

CPWAIT ; wait for effect

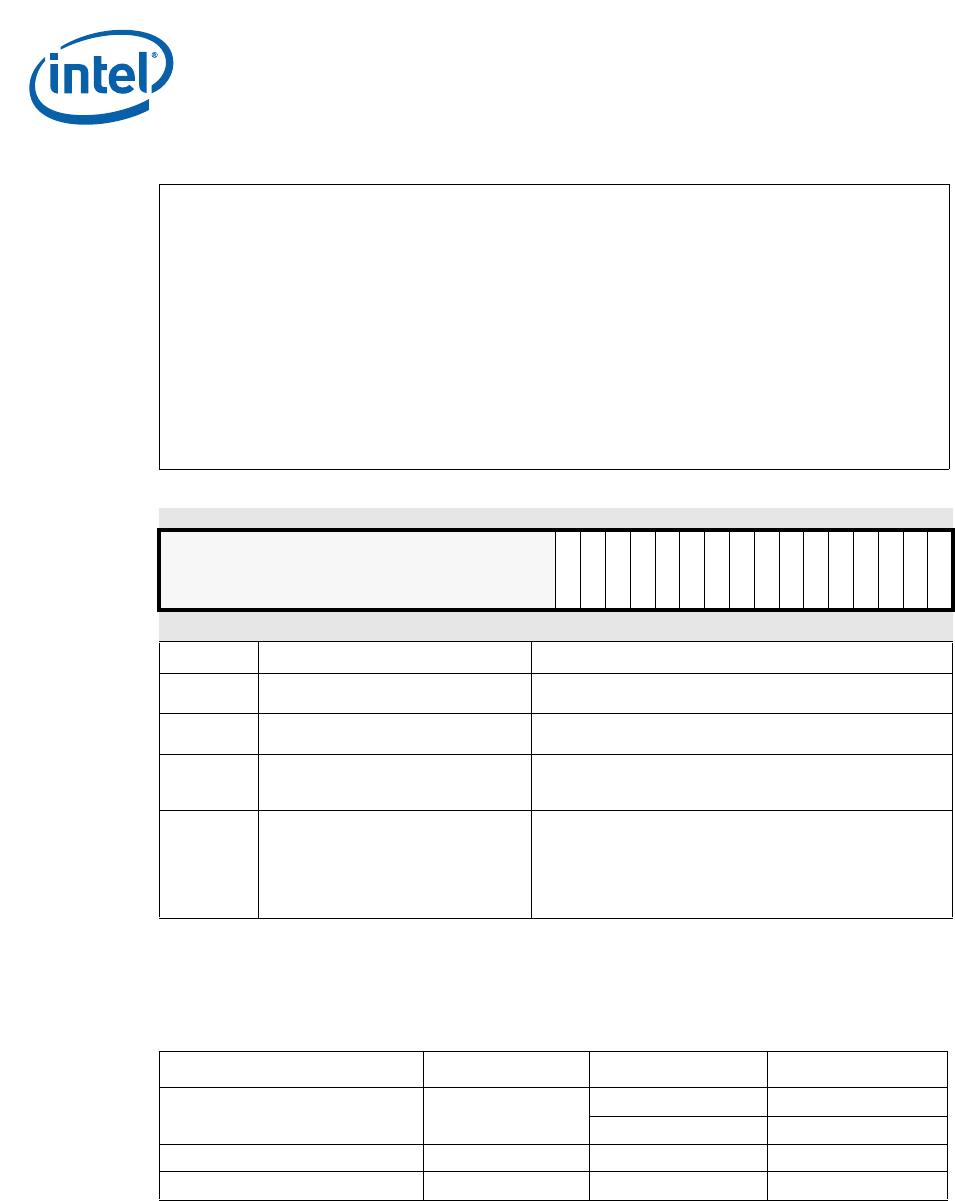

Table 26. Coprocessor Access Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0

C

P

1

3

C

P

1

2

C

P

1

1

C

P

1

0

C

P

9

C

P

8

C

P

7

C

P

6

C

P

5

C

P

4

C

P

3

C

P

2

C

P

1

C

P

0

reset value: 0x0000,0000

Bits Access Description

31:16 Read-unpredictable / Write-as-Zero

Reserved - Should be programmed to zero for future

compatibility

15:14 Read-as-Zero/Write-as-Zero

Reserved - Should be programmed to zero for future

compatibility

13:1 Read / Write

Coprocessor Access Rights-

Each bit in this field corresponds to the access rights for

each coprocessor.

0Read / Write

Coprocessor Access Rights-

This bit corresponds to the access rights for CP0.

0 = Access denied. Any attempt to access the

corresponding coprocessor will generate an

undefined exception.

1 = Access allowed. Includes read and write accesses.

Table 27. CP14 Registers

Description Access Register# (CRn) Register# (CRm)

Performance Monitoring Read / Write

0,1,4,5,8 1

0-3 2

Clock and Power Management Read / Write 6-7 0

Software Debug Read / Write 8-15 0